# A W-Band Phase-Shifter-Embedded PA in 40-nm CMOS for 6G Applications

Chun Wang<sup>#</sup>, Pin-Chun Chiu<sup>&</sup>, Chun-Hsing Li<sup>&</sup>

\*Department of Engineering and System Science, National Tsing Hua University, Hsinchu, Taiwan \*Department of Electrical Engineering, National Taiwan University, Taipei, Taiwan chunhsingli@ntu.edu.tw

Abstract—A phase-shifter-embedded ( $\Delta \varphi$ -embedded) power amplifier (PA) incorporating multifunctional  $\Delta \varphi$ -embedded impedance matching networks (IMN) is proposed for 6G applications. The  $\Delta \varphi$ -embedded IMN can realize impedance transformation, execute a single-ended to differential conversion, and simultaneously provide a phase shift without requiring additional circuits. Hence, the insertion loss, occupied chip area, and power dissipation can be reduced. Realized in a 40-nm digital CMOS process, the proposed PA can provide a maximum saturated output power of 10.2 dBm and a phase-shifting range wider than 90° from 75 to 89 GHz. The power consumption is 151 mW from a 1.1-V supply.

Keywords—CMOS, coupled resonators, W-band, phase shifter, 6G.

### I. Introduction

Terahertz (THz) science and technology have attracted significant attention recently. It has been considered a strong candidate for the sixth-generation (6G) high-speed wireless communication system to supply a data rate higher than 100 Gb/s [1]. To tackle the problem of high path loss at THz frequencies, phased-array technology is a must. The signals radiated and accepted by regularly-deployed transmitters and receivers, respectively, are combined in the desired directions, increasing the phased array's equivalent isotropically-radiated power and signal-to-noise ratio.

LO-phase-shifting architectures are usually adopted for sub-THz/THz phased-array transceivers [2]. The required LO signals for frequency up-/down-conversion are generated by an amplifier-frequency-multiplier chain (AMC) whose first stage is a phase shifter for controlling the signal's phase. However, the frequency multiplication ratio N of the prior AMC works is large, for instance, N=8 in [2] and N=9 in [3], which occupies a large chip area and dissipates a high dc power due to the cascade of many phase shifters, power amplifiers (PA), and frequency multipliers. Moreover, the phase resolution and phase noise of the generated LO signals are degraded by N and 20LogN, respectively. In this work, a phase-shifter-embedded ( $\Delta \varphi$ -embedded) W-band PA incorporating multifunctional  $\Delta \varphi$ embedded impedance matching networks (IMN) is proposed for sub-THz/THz phased-array applications. The proposed  $\Delta \varphi$ embedded IMN can use a single circuit to realize versatile functions of impedance transformation, single-ended to differential conversion, and phase shifts simultaneously. Therefore, the proposed W-band PA not only occupies a small chip area but can also be exploited to generate a phasecontrolled sub-THz/THz LO signal with high output power and

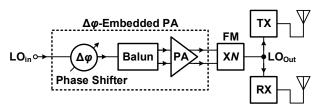

Fig. 1. LO-phase-shifting phased-array transceiver with the proposed  $\Delta \phi$  embedded PA for the LO generation.

fine phase resolution. Realized in a 40-nm digital CMOS process without ultra-thick metal (UTM) layers available, the proposed PA can deliver a maximum saturated output power of 10.2 dBm and simultaneously provide a phase-shifting range  $\Delta \varphi$  wider than 90° from 75 to 89 GHz. The proposed PA could be integrated with a frequency quadrupler to realize a 300-356-GHz LO signal with a full 360° continuously-tuned  $\Delta \varphi$  for the 6G applications. The following sections will explain the design details of the proposed  $\Delta \varphi$ -embedded W-band PA.

## II. PROPOSED $\Delta \varphi$ -EMBEDDED W-BAND PA

### A. LO-Phase-Shifting Phased-Array Architecture

Fig. 1 shows a typical architecture of LO-phase-shifting phased-array transceivers for sub-THz/THz applications. The phase-shifting function is implemented on the LO path by an AMC which cascades a phase shifter, a balun for a single-ended to differential conversion, a PA, and a frequency multiplier (FM) with a frequency multiplication ratio of N. In this work, a small number of 3 and 4 can be chosen for N to generate the required sub-THz/THz LO signals, implying that the chip area, power dissipation, and degradation of the phase resolution and phase noise can be reduced. Moreover, the functions of phase shifts, impedance transformation, and balun can be realized using a single  $\Delta \varphi$ -embedded PA circuit whose design target is to provide high output power and a phase-shifting range wider than 90°. Thus, as the proposed PA is integrated with a ×4 FM, a THz LO signal with a full 360° continuously phase-shifting range can be obtained.

## B. Δφ-embedded PA

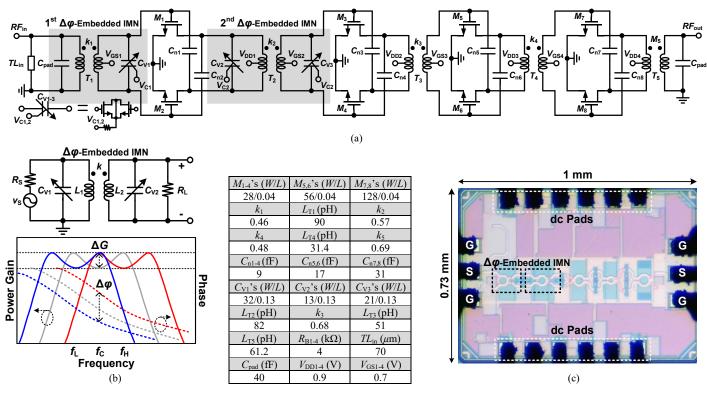

Fig. 2(a) illustrates the proposed  $\Delta \varphi$ -embedded W-band PA realized in a 40-nm digital CMOS without UTM layers available. The distance from the 0.85- $\mu$ m thick top metal layer to the lossy silicon substrate is only 4.1  $\mu$ m, leading to the passive components with much higher loss than that of an RF process with UTM layers. The proposed PA biased in a class-

Fig. 2. (a) Proposed Δφ-embedded W-band PA. (b) Proposed multifunctional Δφ-embedded IMN. (c) Chip photo of the proposed Δφ-embedded W-band PA.

A region comprises four amplifier stages whose transistor size is designed to have a ratio of roughly  $M_{1-2}:M_{3-4}:M_{5-6}:M_{7-8}=$ 1:1:2:4 to deliver a high output power as well as high gain.  $M_{7-}$ 8 can provide an ideal saturated output power of 13 dBm as the power-matched condition is fulfilled. Neutralization capacitors  $C_{\rm n1-8}$  are added to increase the PA's gain and stability. The interstage impedance matchings between the second and third and third and fourth stages are achieved by transformers  $T_3$  and  $T_4$ , respectively. The output transformer  $T_5$  is employed to transform a 50- $\Omega$  load to the optimal impedance  $Z_{\text{opt}}$  of 9.2+14.4j  $\Omega$  to obtain the maximum output power.  $T_5$  also works as a balun to convert a differential output to a singleended one. The simulated amplitude and phase imbalances of the  $T_5$  balun are smaller than 1 dB and 5°, respectively, from 75 to 99 GHz. The proposed multifunctional  $\Delta \varphi$ -embedded impedance matching networks,  $1^{st}$  and  $2^{nd}$   $\Delta \varphi$ -embedded IMNs, are utilized to achieve the impedance-matched conditions at the input and between the first and second stages and simultaneously provide phase shifts, respectively. Moreover, the 1<sup>st</sup>  $\Delta \varphi$ -embedded IMN can also function as a balun.

The operation principle of the proposed  $\Delta \varphi$ -embedded IMN can be explained in Fig. 2(b). It comprises two LC resonators coupled magnetically, i.e., inductively-coupled resonators. A transformer is used to realize the coupled inductors, which implies that the ICR can also work as a balun. The capacitors  $C_{V1}$  and  $C_{V2}$  are implemented by varactors whose capacitance values can be tuned by a control voltage  $V_C$ .  $R_S$  and  $R_L$  model the source and load resistances, respectively. The typical power gain and phase frequency responses of an ICR are shown in Fig. 2(b). The ICR possesses two resonance frequencies,  $f_L$  and  $f_H$ , leading to a broadband frequency response [4]. As the

conditions of  $L_1C_{V1} = L_2C_{V2}$  and  $n^2 = R_S/R_L$  are satisfied, the ICR can conduct an impedance transformation from  $R_S$  to  $R_L$  with the lowest insertion loss at  $f_L$  and  $f_H$  simultaneously. The gain flatness  $\Delta G$  between  $f_L$  and  $f_H$  is determined by the coupling coefficient k of the transformer and the quality factor Q defined as  $R_S\omega_0C_{V1} = R_L\omega_0C_{V2}$  where  $\omega_0$  is  $1/\sqrt{L_1C_{V1}(1-k^2)} =$  $1/\sqrt{L_2C_{V2}(1-k^2)}$  [4]. As  $C_{V1}$  and  $C_{V2}$  are tuned by  $V_C$ ,  $f_L$  and  $f_{\rm H}$  are changed accordingly, resulting in the frequency shift of the gain peaks and the change of the signal phase. As indicated in Fig. 2(b),  $f_L$  and  $f_H$  are designed to keep the operation frequency  $f_C$  between  $f_L$  and  $f_H$  as  $C_{V1}$  and  $C_{V2}$  are varied. By doing this, the ICR can provide a phase shift  $\Delta \varphi$  with a gain variation  $\Delta G$ . Therefore, the proposed  $\Delta \varphi$ -embedded IMN can simultaneously realize a single-ended to differential conversion, impedance transformation, and phase shifts without requiring additional circuits.

In this work, the 1<sup>st</sup> and 2<sup>nd</sup>  $\Delta \varphi$ -embedded IMNs are designed to contribute phase shifts  $\Delta \varphi_1$  and  $\Delta \varphi_2$  larger than 45° at 85 GHz, respectively, leading to a total phase shift wider than 90°. For the 1<sup>st</sup>  $\Delta \varphi$ -embedded IMN design, since the primary coil of  $T_1$  is connected to the input pad where the signal is single-ended, the advantage of a virtual-short condition cannot be employed. Adding a varactor here will require many lossy dc-blocking capacitors to bias the varactor, greatly increasing insertion loss. Hence, only the capacitor on the secondary coil of  $T_1$  is replaced by a variable capacitor  $C_{V1}$ . To achieve the required  $\Delta \varphi_1$  of 45°,  $C_{V1}$  shall be varied from 36 to 56 fF to tune  $f_L$  and  $f_H$  from 81 to 85 GHz and 85 to 89 GHz, respectively. Fortunately, the parasitic capacitances from the input of the first stage, the probing pads, and the transformer itself can be

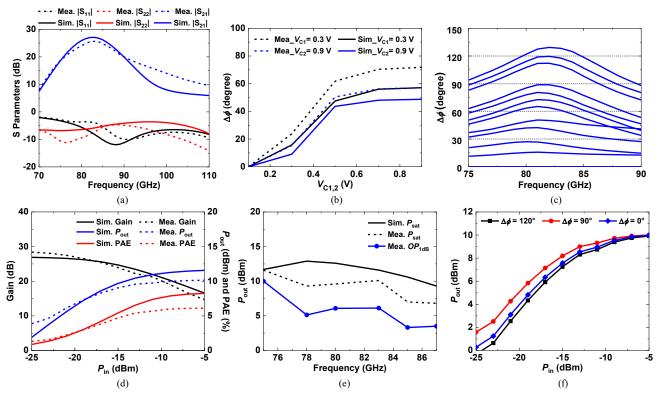

Fig. 3. (a) Measured S parameters. (b) Measured output phase as  $V_{C1}$  and  $V_{C2}$  are changed. (c) Measured frequency response of the output phase. (d) Measured gain,  $P_{\text{out}}$ , and PAE versus the input power  $P_{\text{in}}$ . (e) Measured frequency response of  $P_{\text{sat}}$  and  $OP_{\text{1dB}}$ . (f) Measured  $P_{\text{out}}$  versus  $P_{\text{in}}$  under different phase states:

absorbed into the ICR design. Therefore, C<sub>V1</sub> only needs to change from 14 to 34 fF. NMOS transistors are employed to realize the varactors. The width and length of the transistor for realizing  $C_{V1}$  are designed at 32 and 0.13  $\mu$ m, respectively. The simulated  $\Delta \varphi_1$ ,  $\Delta G$ , and the minimum insertion loss of the 1<sup>st</sup>  $\Delta \varphi$ -embedded IMN are 47°, 2.2 dB, and 7.2 dB at 85 GHz, respectively, as  $V_{C1}$  is varied from 0.1 to 0.9 V and  $V_{GS1}$  is 0.7 V. The simulated amplitude and phase imbalances of the 1<sup>st</sup>  $\Delta \varphi$ embedded IMN's differential output are smaller than 1 dB and 5°, respectively, from 75 to 110 GHz. For the  $2^{nd} \Delta \varphi$ -embedded IMN design, the varactors  $C_{V2}$  and  $C_{V3}$  shall be varied from 26 to 39 fF to achieve  $\Delta \varphi_2$  of 55°. Note that  $\Delta \varphi_2$  is designed 10° wider than the required 45° to have enough phase-shifting margin since the 1<sup>st</sup>  $\Delta \varphi$ -embedded IMN only has a single tuning varactor.  $C_{V2}$  and  $C_{V3}$  only need to change from 7 to 16 fF after taking the parasitic capacitances from the transformer and the output and input of the first and second stages into the ICR design. Since the common-mode dc voltages of  $V_{\rm DD1}$  and  $V_{\rm GS2}$ on the primary and secondary coils of  $T_2$  are 0.9 and 0.7 V, respectively, the tuning ranges of  $C_{V2}$  and  $C_{V3}$  with the same control voltage  $V_{C2}$  are different. To obtain the same capacitance tuning range, the width and length of the transistors for realizing  $C_{V2}$  and  $C_{V3}$  are designed at 13 and 0.13  $\mu$ m and 21 and 0.13  $\mu$ m, respectively. The simulated  $\Delta \varphi_2$ ,  $\Delta G$ , and the minimum insertion loss of the  $2^{nd} \Delta \varphi$ -embedded IMN are 57°, 3.4 dB, and 5.5 dB at 85 GHz, respectively, as  $V_{C2}$  is varied from 0.1 to 0.9 V and  $V_{\rm GS1}$  is fixed at 0.7 V, which meets the requirement. Finally, a transmission line TLin with a length of 70  $\mu$ m is added to minimize the parasitic effect caused by the

probing pads. With the proposed  $\Delta \varphi$ -embedded IMNs, the proposed  $\Delta \varphi$ -embedded W-band PA can provide a simulated small signal gain of 27.1 dB, an output 1-dB compression point  $OP_{1dB}$  of 8 dBm, a saturated output power  $P_{sat}$  of 11.6 dBm, and a phase-shifting range larger than 90° from 74 to 86 GHz.

## III. EXPERIMENTAL RESULTS

The proposed  $\Delta \varphi$ -embedded W-band PA is realized in a 40-nm digital CMOS process without UTM layers available. The chip photo is shown in Fig. 2(c). The measurement is conducted by an on-wafer setup where the input and output high-frequency signals  $RF_{\rm in}$  and  $RF_{\rm out}$  are applied and acquired through GSG probes, respectively, while dc biases are given by PGPPGP dc probes. The proposed W-band PA consumes 151 mW from a 1.1-V supply.

The measured S parameters are illustrated in Fig. 3(a). The proposed PA can provide a peak  $|S_{21}|$  of 25.7 dB at 83 GHz with a 3-dB bandwidth from 79 to 87 GHz as  $V_{\text{DD}1.4}$  and  $V_{\text{GS}1.4}$  are 0.9 and 0.7 V, respectively. As shown in Fig. 3(b), the measured  $\Delta \varphi_1$  and  $\Delta \varphi_2$  at 83 GHz as  $V_{\text{C1}}$  and  $V_{\text{C2}}$  are varied from 0.1 to 0.9 V, and  $V_{\text{GS}1}$  is changed to 0.8 V are 57.1 and 71.8°, respectively, resulting in a maximum  $\Delta \varphi$  of 128.9° with  $\Delta G$  of 4.2 dB. The measured  $\Delta \varphi$  is larger than the simulated one due to the capacitance variation of the varactors. It is found that each varactor roughly contributes an 8° difference. The measured frequency response of the phase shift is depicted in Fig. 3(c). A maximum  $\Delta \varphi$  of 128.9° is measured at 83 GHz while keeping  $\Delta \varphi$  wider than 90° from 75 to 89 GHz when  $V_{\text{C1}}$  and  $V_{\text{C2}}$  are changed from 0.1 to 0.9 V, respectively. The phase

Table 1. Performance Summary and Comparison with Prior Works

| Reference                                           | JSSC'22 [5]       | TMTT'21 [6]    | MWCL'20 [7]   | MWCL'20 [8] | TMTT'15 [9]    | This work           |

|-----------------------------------------------------|-------------------|----------------|---------------|-------------|----------------|---------------------|

| CMOS Technology                                     | 65 nm             | 28-nm SOI      | 40 nm         | 65 nm       | 40 nm          | 40-nm               |

| UTM Available                                       | Yes               | Yes            | Yes           | Yes         | Yes            | No                  |

| Topology                                            | 8-way diff.(a) CS | 1-way diff. CS | 2-way Cascode | 2-way CS    | 4-way diff. CS | 1-way diff. CS      |

| $V_{ m DD}\left({ m V} ight)$                       | 1.2               | 1              | 1.8           | 1.2         | 0.9            | 1.1                 |

| $f_0$ (GHz)                                         | 84                | 77             | 110           | 77          | 70.3-85.5      | 83                  |

| $G_{\mathbb{P}}\left(\mathrm{dB}\right)$            | 29.3              | 26.5           | 25.5          | 26.4        | 18.1           | 25.7 <sup>(c)</sup> |

| OP <sub>1dB</sub> (dBm)                             | 16.2              | 10             | 10.3          | 11.5        | 17.8           | 6.1                 |

| P <sub>sat</sub> (dBm)                              | 19.1              | 13.5           | 12.2          | 15.8        | 20.9           | 10.2                |

| Estimated P <sub>sat,1-way,wi-PS</sub> (b) (dBm)    | 3.1               | 6.5            | -0.8          | 5.8         | 7.9            | 10.2                |

| PAE (%)                                             | 8.6               | 14.5           | 8.5           | 15.9        | 22.3           | 6.6                 |

| $\Delta \varphi / \Delta G  (^{\circ}/\mathrm{dB})$ | 0                 | 0              | 0             | 0           | 0              | 128.9/4.2           |

| $P_{dc}(W)$                                         | 0.582             | 0.15           | -             | 0.24        | 0.375          | 0.151               |

| Chip Area (mm2)                                     | 0.72              | 0.14           | 0.24          | 0.14        | 0.57           | 0.73                |

(a) Differential. (b) Estimated 1-way  $P_{\text{sat}}$  with a phase shifter  $P_{\text{sat,1-way,wi,PS}} = P_{\text{sat}} - 10\text{Log}N_{\text{C}} - 6 \text{ dB}$ , where  $N_{\text{C}}$  is the number of the power-combining ways assuming the power-combing network is lossless, and 6 dB is the insertion loss of a 90° phase shifter reported in [10]. (c)  $V_{\text{DD4}} = 0.9 \text{ V}$ .

can be continuously tuned by  $V_{C1}$  and  $V_{C2}$  within the 128.9° phase-shifting range. Note that with the measured  $\Delta \varphi$  wider than the simulated one, the proposed  $\Delta \varphi$ -embedded W-band PA can also be integrated with a ×3 FM to generate a 225-267-GHz sub-THz LO signal with a full 360° continuously phase-shifting range. The measured  $OP_{1dB}$  and the power-added efficiency (PAE) at 83 GHz are depicted in Fig. 3(d) as  $V_{\rm DD4}$  is changed to 1.1 V. The proposed PA can provide  $P_{\text{sat}}$  of 10.2 dBm and *OP*<sub>1dB</sub> of 6.6 dBm with a peak PAE of 6.6%. Fig. 3(e) depicts the measured frequency responses of  $P_{\text{sat}}$  and  $OP_{\text{1dB}}$ .  $P_{\text{sat}}$  has a peak value of 11.6 dBm at 75 GHz and decreases to 6.8 dBm at 87 GHz. The measured  $P_{\text{out}}$  versus the input power  $P_{\text{in}}$  under the phase states of 0, 90, and 120° is indicated in Fig. 3(f). The variation of P<sub>sat</sub> is only 0.1 dB within a 120° phase-shifting range. The performance of the proposed  $\Delta \varphi$ -embedded PA and its comparison with prior works are summarized in Table 1. The proposed PA without UTM layers available can provide a compatible output power while providing a phase shift of 128.9° at 83 GHz with a  $\Delta \varphi$  wider than 90° from 75 to 89 GHz. To the best of the authors' knowledge, the proposed PA is the first work that can provide an additional phase-shifting function reported thus far. With the advantageous phase-shifting function, the proposed PA can be a strong candidate to realize a phase-controllable LO signal for 6G LO-phase-shifting phased-array transceivers.

## IV. CONCLUSION

A phase-shifter-embedded ( $\Delta \varphi$ -embedded) W-band PA is proposed and successfully verified by experimental results. The phase-shifting function is enabled by integrating the proposed multifunctional  $\Delta \varphi$ -embedded impedance matching networks, which can simultaneously realize a single-ended to differential conversion, impedance matching, and phase shifts without requiring additional c. Realized in a 40-nm digital CMOS process, the proposed PA can deliver a saturated output power of 10.2 dBm and a maximum phase-shifting range  $\Delta \varphi$  of 128.9° at 83 GHz while maintaining  $\Delta \varphi$  wider than 90° from 75 to 89 GHz.

### ACKNOWLEDGMENT

This work was jointly funded by the National Science and Technology Council (NSTC), Taiwan, under Grant MOST 110-2221-E-002-053-MY2, MOST 111-2221-E-002-094-MY3, NSTC 111-2218-E-002-025, NSTC 111-2622-8-A49-018-SB, and MOST 111-2218-E-002-030, and National Taiwan University, Taiwan, under Grant NTU-CC-112L893305. The authors would also like to acknowledge Taiwan Semiconductor Research Institute (TSRI), Hsinchu, Taiwan, for the chip fabrication and measurement.

### REFERENCES

- IEEE Standard for High Data Rate Wireless Multi-Media Networks— Amendment 2: 100 Gb/s Wireless Switched Point-to-Point Physical Layer, IEEE Standard 802.15.3d–2017, 2017.

- [2] I. Abdo et al., "A bi-directional 300-GHz-band phased-array transceiver in 65-nm CMOS with outphasing transmitting mode and LO emission cancellation," *IEEE J. Solid-State Circuits*, vol. 57, no. 8, pp. 2292–2308, Aug. 2022.

- [3] S. Hara et al., "A 76-Gbit/s 265-GHz CMOS receiver with WR-3.4 waveguide interface," IEEE J. Solid-State Circuits, vol. 57, no. 10, pp. 2988–2998, Oct. 2022.

- [4] C.-H. Li et al., "A 1.2-V 5.2-mW 20–30-GHz wideband receiver frontend in 0.18-µm CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 11, pp. 2823-2832, Nov. 2014.

- [5] V.-S. Trinh and J.-D. Park, "An 85-GHz power amplifier utilizing a transformer-based power combiner operating beyond the self-resonance frequency," *IEEE J. Solid-State Circuits*, vol. 57, no. 3, pp. 882–891, Mar. 2022.

- [6] C. Nocera, G. Papotto, A. Cavarra, E. Ragonese, and G. Palmisano, "A 13.5-dBm 1-V power amplifier for W-Band automotive radar applications in 28-nm FD-SOI CMOS technology," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 3, pp. 1654–1660, Mar. 2021.

- [7] G. Cho, J. Park, and S. Hong, "A 25.5-dB peak gain F-band power amplifier with an adaptive built-in linearizer," *IEEE Microw. Wireless Compon. Lett.*, vol. 30, no. 1, pp. 106–108, Jan. 2020.

- [8] L. Chen, L. Zhang, and Y. Wang, "A 26.4-dB gain 15.82-dBm 77-GHz CMOS power amplifier with 15.9% PAE using transformer-based quadrature coupler network," *IEEE Microw. Wireless Compon. Lett.*, vol. 30, no. 1, pp. 78–81, Jan. 2020.

- [9] D. Zhao and P. Reynaert, "An E-band power amplifier with broadband parallel-series power combiner in 40-nm CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 2, pp. 683–690, Feb. 2015.

- [10] M. Yaghoobi, M. H. Kashani, M. Yavari, and S. Mirabbasi, "A 56-to-66 GHz CMOS low-power phased-array receiver front-end with hybrid phase shifting scheme," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 67, no. 11, pp. 4002–4014, Nov. 2020.