# A *Ka*-band 35-dBm P<sub>0.1dB</sub> Low-loss Monolithic SPDT Switch using Anti-series Diode Connection

Jung Chou, Wei-Cheng Chen, Yong-Le Wang, Yi-Fu Chen, Hong-Yeh Chang Depart. of Electrical Engineering, National Central University, Taiwan hychang@ee.ncu.edu.tw

Abstract—In this paper, a Ka-band monolithic high-power low-loss single-port double-throw (SPDT) switch is proposed using a GaAs PIN process. The switch is designed using an innovative anti-series diode connection to significantly enhance 1-dB compression point, since the turned-on issue of the diode can be effectively resolved under high-power driving. Between 25 and 30 GHz, the proposed SPDT switch features a measured insertion loss of within 1.2 dB, an isolation of higher than 20 dB, and an input 0.1-dB compression point (PoldB) of higher than 35 dBm. As compared with prior art, this work is suitable for high-power applications in microwave and millimeter-wave bands due to its superior performance and compact chip size.

*Keywords*— Diode, GaAs, microwave and millimeter-wave (mm-wave), PIN, switch.

## I. INTRODUCTION

Demand of the modern wireless communications, a highpower low-loss high-isolation switch is crucial for the transceiver, especially for millimeter-wave (mm-wave) 5G mobile applications [1]. Several circuit topologies, including traveling-wave [2]-[5], series-shunt [6]-[8], absorptive-type [9], quarter-wavelength  $(1/\lambda)$  shunt [10], and impedance transformation [11], can be employed to achieve low insertion loss and high isolation up to mm-wave bands. The active device can be based on high electron-mobility transistors (HEMTs) [2], [4]-[6], [11], CMOS [3], and PIN diodes [7]-[10]. A single-pole double-throw (SPDT) switch is usually connected among the antenna, transmitter, and receiver, for the time-division multiplexing, and the 1-dB or 0.1-dB compression point (P<sub>1dB</sub> or  $P_{0.1dB}$ ) of the switch is a key specification for the transmitting operation since it limits the maximum RF output power. The input P<sub>1dB</sub> of the GaAs HEMT or CMOS switch is usually lower than 30 dBm due to the device characteristic, and the SiGe- or GaAs-based PIN-diode switch is also limited due to the rectified dc current with RF power driving.

To further enhance the P<sub>1dB</sub>, a switch using stacked transistors with sub-design rule channel length in floated p-wells was proposed in [13], but the maximum power handling would be limited by an abrupt output drop. A switch using stacked FETs with feed-forward capacitors in floated well was proposed to achieve a power handling of up to 33 dBm at 1.8 GHz [14], and it would be limited for mm-wave design due to the parasitic effect. The P<sub>1dB</sub> can also be enhanced using a negative body bias technique [3], but the maximum power handling is still limited. In this paper, a *Ka*-band monolithic SPDT switch is proposed using a GaAs PIN diode process. With an innovative anti-series diode connection, the proposed

switch features a measured insertion loss of within 1.2 dB, an isolation of higher than 20 dB, and an input  $P_{0.1dB}$  of higher than 35 dBm between 25 and 30 GHz. As compared with the previously reported monolithic PIN-diode switches, the power handling of the switch can be significantly enhanced due to the cancellation of the rectified dc current under high-power driving.

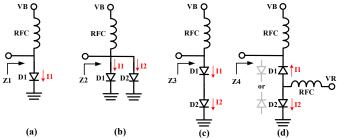

Fig. 1. Circuit topologies for the load impedance of the switch, (a) single diode, (b) parallel diodes, (c) series diodes, and (d) proposed anti-series diodes.

# II. CIRCUIT DESIGN AND ANALYSIS

The GaAs PIN diode process provided by WIN Semiconductors Corporation, Taiwan is adopted for designing the proposed SPDT switch. When the diode size is  $10\times10~\mu\text{m}^2$ , the turn-on resistance and turn-off capacitance are 3  $\Omega$  and 25 fF, respectively. In general, the diode can be a series or shunt element for the switch design. The diode is turned on and off with and without dc bias current, respectively. For the series connection, the insertion loss increases with increasing the turn-on resistance, and the isolation decreases with increasing the turn-off capacitance. For the shunt connection, the insertion loss increases with increasing the turn-off capacitance, and the isolation decreases with increasing the turn-off capacitance, and the isolation decreases with increasing the turn-on resistance.

Under the small-signal condition, the input impedance of the diode would be very high when the diode is turned off without dc bias current. With increasing the RF input power, the input impedance decreases due to the rectification, therefore, the insertion loss (or  $P_{1dB}$ ) and isolation are both degraded under the high-power condition. Four circuit topologies, including single diode, parallel diodes, series diodes, and proposed antiseries diodes, are shown in Fig. 1 for the load impedance of the switch, where I1 and I2 are the rectified dc currents of D1 and D2, respectively. When the dc bias VB is 0 V, the simulated input impedance for the single diode significantly decreases with increasing the RF power up to 30 dBm. The turn-on effect of the diode can be suppressed with reversed dc bias (VB = -6 V). The simulated results of the parallel diodes and series

diodes are similar to the single diode, and the simulated impedances of the parallel diodes and the series diodes are lower and higher than the single diode, respectively, under the high power condition. The simulated impedances of the proposed anti-series diodes still decreases with increasing the RF power and the simulated results is similar to the series diodes. To further suppress the turn-on effect, the diodes D1 and D2 can be biased both in the revised dc condition, such as  $VB = 0 \ V$  and  $VR = -6 \ V$ . The rectified dc currents I1 and I2 would be suppressed by decreasing VR to negative voltage, and therefore, the D1 and D2 could be kept in the turn-off condition under the high-power driving. Also, the high input impedance can be maintained well with a floating VR due to the cancellation of I1 and I2.

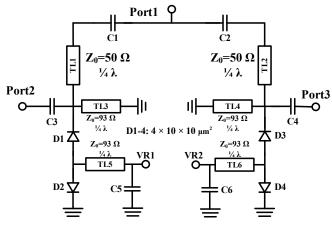

Fig. 2. Schematic of the proposed SPDT switch.

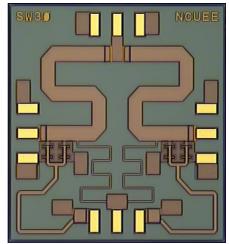

Fig. 3. Chip photo of the proposed SPDT switch with a chip size of  $1\times1$  mm<sup>2</sup>.

The schematic of the proposed SPDT switch is shown in Fig. 2, and the circuit is based on the quarter-wavelength shunt topology with the anti-series diodes D1-4 to minimize the insertion loss. The quarter-wavelength transmission lines TL1-2 perform the impedance transformation, and the transmission lines TL3-6 perform the RF choke and the dc bias networks. The capacitors C1-C4 and C5-6 perform the dc block and RF bypass networks, respectively. When the path between Port1 and Port2 (Port3) is turned on (off), the dc biases VR1 and VR2

are low state ( $\leq 0$  V) and high state (>1.3 V), and the diodes D1-2 and D3-4 are off- and on-state, respectively. The simulated input P<sub>1dB</sub> and third-order intercept point (IP3) versus low-state voltage VR of the proposed SPDT switch at 28 GHz can be further enhanced by lowering the low-state voltage VR1 (or VR2). The chip photo of the proposed SPDT switch is shown Fig. 3 with a chip size of  $1\times1$ mm<sup>2</sup>.

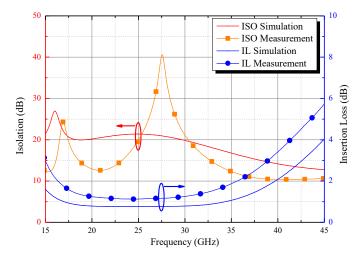

Fig. 4. Simulated and measured insertion losses (IL) and isolations (ISO) of the proposed SPDT switch.

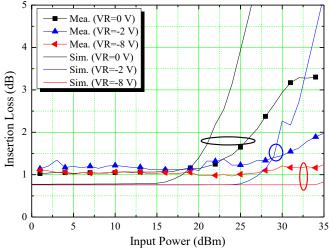

Fig. 5. Simulated and measured insertion losses versus input power with various VR at 28 GHz for the proposed SPDT switch.

# III. EXPERIMENTAL RESULTS AND DISCUSSIONS

The proposed SPDT switch is characterized via on-wafer probing. For the small-signal S-parameters measurement, a Keysight N5227A vector network analyzer is adopted. When VR1 and VR2 are 0 and 1.3 V, respectively, the simulated and measured insertion losses between Port1 and Port 2, and isolations between Port1 and Port 3 are plotted in Fig. 4. From 25 to 30 GHz, the proposed SPDT switch features a measured insertion loss of within 1.2 dB and a measured isolation of better than 20 dB. When VR1 is varying from 0 to -8 V, the measured insertion loss and isolation are almost the same. For

| Table 1  | Darfarmanaa | aamnarican | of the | prior o | rt and this work |

|----------|-------------|------------|--------|---------|------------------|

| Table 1. | Periormance | comparison | or the | prior a | rt and this work |

| Ref. | Process       | Topology            | Freq. (GHz) | IL (dB)       | ISO (dB)  | P <sub>1dB</sub> (dBm) | $P_{DC}(mW)$ | Chip size (mm <sup>2</sup> ) |

|------|---------------|---------------------|-------------|---------------|-----------|------------------------|--------------|------------------------------|

| [4]  | InGaAs mHEMT  | SPST Traveling-wave | DC - 30     | <5.5          | >32       | >20                    | 0            | $0.85 \times 1.8$            |

| [5]  | InGaAs PIN    | Traveling-wave      | 25 - 95     | <3.2          | >40       | N/A                    | 144          | $1.05 \times 0.58$           |

| [6]  | GaN HEMT      | Series-shunt        | 2 - 18      | < 2.1         | > 30      | 33                     |              | $1.5 \times 1.1$             |

| [7]  | SiGe PIN      | Series-shunt        | 38 - 67     | 2.0           | >23       | 22                     | 7.5          | 0.066                        |

| [8]  | GaAs PIN      | Series-shunt        | 0.01 - 70   | <2            | 20@38 GHz | 25.5@2 GHz             |              | $0.74 \times 0.57$           |

| [9]  | GaN PIN       | Absorptive-type     | 20 - 27     | < 3.4         | > 12.5    | N/A                    | 90           | $2.57 \times 1.03$           |

| [10] | SiGe PIN      | 1/4λ shunt          | 73 - 113    | <2            | 19 - 22   | >24                    | 10.2         | 0.14                         |

| [14] | 65nm CMOS     | Series-shunt        | 25 – 30     | RX: 0.74-1.16 | >16.4     | 5.2                    | 0            | $0.14 \times 0.31$           |

|      |               |                     |             | TX: 0.96-1.1  | >27.0     | 31.8                   |              |                              |

| [15] | GaN HEMT      | 1/4λ shunt          | 110 - 170   | 1.8-2.3       | 29-38     | >33                    |              | $1.5 \times 1$               |

| [16] | InGaAs mHEMT  | 1/4λ shunt          | 50 - 75     | 1-1.6         | 31.6-32.8 | >22                    | 0            | 1.5 × 1                      |

| This | GaAs PIN      | 1/4λ TL with        | 25 – 30     | <1.2          | > 20      | >35                    | 91.7         | 1×1                          |

| work | work GaAs PIN | anti-series PIN     | 23 – 30     | <u>~1.2</u>   | - 20      | $(P_{0.1dB})$          | 91./         | 1 1 1                        |

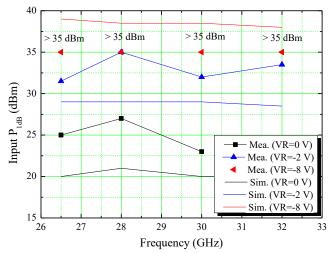

the large-signal characterization, a Keysight E8257D signal generator with a power amplifier is adopted as the input signal, and an Agilent E4448A spectrum analyzer with an attenuator is employed for receiving the output power. The simulated and measured insertion losses versus input power with various VR at 28 GHz are plotted in Fig. 5 for the proposed SPDT switch. When VR is 0 V, the measured insertion loss increases with increasing the input power, and the measured P<sub>1dB</sub> is 28 dBm. The measured P<sub>1dB</sub> is significantly enhanced by decreasing VR to -8V, and it is higher than 35 dBm. Due to the limitation of the power amplifier, the power handling is only evaluated up to 35 dBm. The simulated and measured input P<sub>1dB</sub> versus frequency is plotted in Fig. 6 with various VR, and the measured P<sub>0.1dB</sub> is higher than 35 dBm over the frequency. Due to the limitation of the instruments, the linearity of the proposed SPDT cannot be measured. The performance comparison of the prior art and this work is summarized in Table 1, and all the works are designed using compound semiconductors. This work has the lowest insertion loss, highest P<sub>1dB</sub> among all the reported microwave and mm-wave monolithic switches.

Fig. 6. Simulated and measured input  $P_{1dB}$  versus frequency with various VR.

### IV. CONCLUSION

A *Ka*-band monolithic high-power low-loss SPDT switch is successfully developed using a GaAs PIN diode process. Based on the proposed anti-series diode connection, the P<sub>1dB</sub> of the switch is significantly enhanced since the rectified dc current of the diodes can be suppressed under the high RF power driving. The proposed circuit topology is also suitable for other semiconductor processes. The demonstrated SPDT switch has the lowest insertion loss and the highest P<sub>1dB</sub> as compared with prior art, and it can be applied for some advanced transceiver applications due to its superior performance.

#### ACKNOWLEDGMENT

The chip was fabricated by WIN Semiconductors Corporation, Taiwan. This work was supported by the National Science and Technology Council (NSTC), Taiwan, under Grant MOST 110-2221-E-008-029-MY3, and the Taiwan Semiconductor Research Institute (TSRI), Hsinchu City, Taiwan. The dc and RF probes are supported by GGB Inc., FL, USA.

#### REFERENCES

- [1] A. G. Roy, O. Inac, A.j Singh, T. Mukatel, O. Brandelstein, T. W. Brown, S. Abughazaleh, J. S. Hayden III, B. Park, G. Bachmanek, T.-Y. J. Kao, J. Hagn, S. Dalmia, D. Shoham, B. Davis, I. Fisher, R. Sover, A. Freiman, B. Xiao, B. Singh, and J. Jensen, "A 37-40 GHz phased array front-end with dual polarization for 5G MIMO beamforming applications," in *Proc. IEEE RFIC*, Jun. 2019, pp. 251-254.

- [2] K.-Y. Lin, W.-H. Tu, P.-Y. Chen, H.-Y. Chang, H. Wang, and R.-B. Wu, "Millimeter-wave MMIC passive HEMT switches using travelingwave concept," *IEEE Trans. Microw. Theory Techn.*, vol. 52, no. 8, pp. 1798– 1808, Aug. 2004.

- [3] H.-Y. Chang, and C.-Y. Chan, "A low loss high isolation DC-60 GHz SPDT traveling-wave switch with a body bias technique in 90 nm CMOS process," *IEEE Microw. Wireless Compon. Lett.*,, vol. 20, no. 02, pp. 82-84. Feb. 2010.

- [4] C.-K. Lin, W.-K. Wang, Y.-J. Chan, and H.-K. Chiou, 'BCB-bridge distributed wideband SPST switch using 0.25-μm In0.5Al0.5As-In0.5Ga0.5As metamorphic HEMTs," *IEEE Trans Electron Devices*, vol. 52, no. 1, pp. 1-5, Jan 2005.

- [5] J. G. Yang and K. Yang, "Broadband InGaAs PIN traveling-wave switch using a BCB-based thin-film microstrip line structure," *IEEE Microw. Wireless Compon. Lett.*, vol. 19, no. 10, pp. 647-649, Oct. 2009.

- [6] N. Billström, J. Nilsson, A. Tengs and N. Rorsman, "High performance GaN front-end MMICs," 2011 6th Euro. Microw. Int. Circuit Conf., Manchester, 2011, pp. 348-351.

- [7] Y. Gong, J. W. Teng, and J. D. Cressler, "A compact, high-power, 60 GHz SPDT switch using shunt-series SiGe PIN diodes," 2019 IEEE Radio Freq. Int. Circuits Sym., pp. 15-18.

- [8] H.-E. Liu, X. Lin, H. Y. Chang, and Y. C. Wang, "10-MHz-to-70-GHz ultra-wideband low-insertion-loss SPST and SPDT switches using GaAs PIN diode MMIC process," 2018 IEEE Asia-Pacific Microw. Conf., pp. 1217-1219.

- [9] J.-G. Yang and K. Yang, "High-linearity K-Band absorptive-type MMIC switch using GaN PIN-diodes," *IEEE Microw. Wireless Compon. Lett.*, vol. 23, no. 1, pp. 37-39, Jan. 2013.

- [10] P. Song, R. L. Schmid, Ahmet Çağrı Ulusoy, J. D. Cressler, "A high-power, low-loss W-band SPDT switch using SiGe PIN diodes," in 2014 IEEE Radio Freq. Int. Circuits Symp., 2014, pp. 195-198.

- [11] K.-Y. Lin, Y.-J. Wang, D.-C. Niu, and H. Wang, "Millimeter-wave MMIC single-pole-double-throw passive HEMT switches using impedance transformation networks," *IEEE Trans. Microw. Theory Techn.*, vol. 51, no. 04, pp. 1076–1085, Apr. 2003.