# An Ultrawideband Transition from Substrate Integrated Suspended Parallel Strip Line to Grounded Coplanar Waveguide

Shutao He, Yongqiang Wang, Kaixue Ma School of Microelectronics, Tianjin University, Tianjin, China wangyongqiang008@tju.edu.cn

Abstract—This paper proposes a novel ultrawideband transition between substrate integrated suspended parallel strip line (SISPSL) and grounded coplanar waveguide (GCPW). Such transition serviceably facilitates the integration of different transmission lines on the same multilayer printed circuit board (PCB) structure, which can easily realize functional fusion. The double-sided parallel strip-line (DSPSL) is embedded inside the air cavity of the self-packaging substrate integrated suspended line (SISL) multilayer structure, which can effectively reduce the radiation loss of the circuit with the electromagnetic shielding property of the enclosure. The proposed transition is fabricated using the PCB process, which has the advantages of self-packaging and low cost. The measured return loss is larger than 10 dB from DC to 60 GHz. It provides a guarantee for the circuit packaging and testing of ultrawideband SISPSL.

Keywords—ultrawideband, transition, double-sided parallel strip-line (DSPSL), substrate integrated suspended line (SISL), substrate integrated suspended parallel strip line (SISPSL), grounded coplanar waveguide (GCPW).

### I. Introduction

Balanced microwave circuits play an important role in wireless communication systems because of their higher common-mode suppression and lower electromagnetic (EM) interference. As a balanced transmission line, double-sided parallel strip-line (DSPSL) has been extensively studied [1]. Because of its wider characteristic impedance range and excellent performance, DSPSL arouse much attention recently in microwave circuit applications such as [2]–[4].

In order to measure the performance of the DSPSL circuits, an efficient transition is required with wide bandwidth. In [5], a transition from microstrip line (MS) to DSPSL is developed with a wide bandwidth from 1 GHz to 30 GHz. In [6], a broadband transition between DSPSL and coplanar waveguide (CPW) is proposed from 1.3 GHz to 9 GHz. In [7], a broadband MS to DSPSL transition is proposed, and the return loss is better than 15 dB from 1.7 GHz to 9.4 GHz. In [8], a millimeterwave transition between waveguide and DSPSL is designed from 31 GHz to 39 GHz. In summary, the bandwidth of existing transitions is still limited, and it is very necessary to obtain a wider bandwidth for DSPSL transition, which can meet the need for DC to millimeter-wave applications measurement. In addition, the DSPSL circuits still have considerable limitations in actual engineering applications. Due to the suspension of two strips of DSPSL, radiation loss is inevitable. Taking into account the packaging issues, the complexity of circuits will be increased and the performance is not easy to keep unaffected.

In this paper, a novel ultrawideband transition between substrate integrated suspended parallel strip line (SISPSL) and grounded coplanar waveguide (GCPW) is proposed from DC

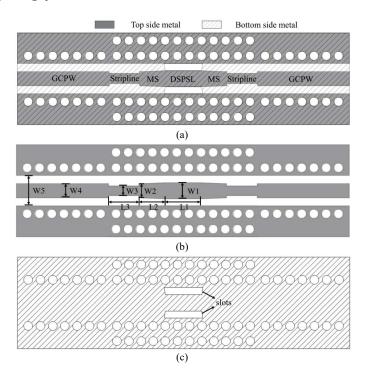

Fig. 1. Layout of the proposed back-to-back transition: (a) Schematic layout of board3; (b) Top side metal of board3; (c) Bottom side metal of board3. (W1 = 0.53 mm, W2 = 0.47 mm, W3 = 0.33 mm, W4 = 0.48 mm, W5 = 1 mm, L1 = 1.2 mm, L2 = 0.83 mm, L3 = 1 mm, Rvia = 0.15 mm.)

to 60 GHz, which can be applied in millimeter-wave band. SISPSL is a platform embedding DSPSL in multilayer substrate integrated suspended line (SISL) [9], which can reduce radiation loss and realize the characteristics of self-packaging and suspension. Therefore, the transition does not need to introduce external metal shielding for packaging, so as to effectively avoid affecting the circuit performance after adding a metal enclosure. This design uses a tapered structure to realize broadband features. Meanwhile, by reducing the size of cavities, the generation of high-order modes is suppressed. Finally, EM field matching and impedance matching are carefully designed to further expand the operating bandwidth of the transition. Compared with other DSPSL-based transitions, the proposed transition outlined in this paper demonstrates improved bandwidth, minimized radiation loss, and self-packaging. The proposed ultrawideband transition can help with the testing and system integration of ultrawideband SISPSL circuits.

## II. TRANSITION DESIGN

The transition consists of four parts, including SISPSL, MS, stripline, and GCPW, as shown in Fig. 1(a). Fig. 1(b) and Fig.

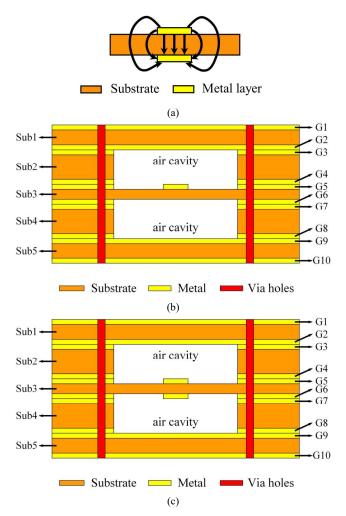

Fig. 2. Cross-sectional views: (a) Conventional DSPSL; (b) Self-packaged SISL platform [10]; (c) Proposed self-packaged SISPSL platform.

1(c) show the top side metal and bottom side metal of board3 of the proposed transition. Among that, the slots are formed between DSPSL and the lateral ground on both sides. The transition in this paper is based on a self-packaged platform, so the radiation loss can be reduced.

Fig. 2(a) illustrates the cross-sectional view and electric field distribution of the conventional DSPSL. The middle substrate generally requires to be suspended for practice application, and there exists radiation loss inevitably. As a result, an additional metal box is needed for shielding and packaging, which makes the whole circuit bulky. Fig. 2(b) shows the cross-sectional view of the self-packaged SISL structure [10]. It is composed of five substrate layers, denoted by Sub1-Sub5, and ten metal layers, denoted by G1-G10. Sub2 and Sub4 are hollowed to form air cavities. As shown in Fig. 2(c), SISPSL embeds DSPSL inside multilayer boards, and it is convenient to achieve suspension of the middle substrate. Therefore, SISPSL is based on the multilayer printed circuit board (PCB) process and becomes self-packaged. Moreover, the EM field will be mainly limited inside air cavities, which helps reduce radiation loss.

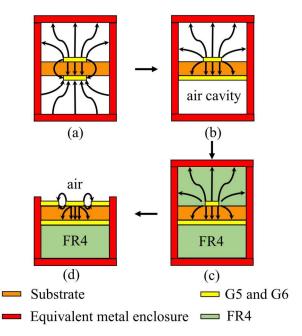

Fig. 3. Electric field distribution of the four parts: (a) SISPSL; (b) MS; (c) stripline; (d) GCPW.

In Fig. 2(c), Sub3 chooses Rogers 4350B with a relative dielectric constant of 3.66 and a thickness of 0.254 mm. The other boards choose low-cost FR4 with a relative dielectric constant of 2.2. The thickness of Sub1 and Sub5 is 0.6 mm. The thickness of Sub2 and Sub4 is 1 mm in which the center part is hollowed out to form two air cavities. The via holes designed on PCB boards and the metal layers of G2 and G9 form an approximate metal enclosure, achieving excellent EM shielding. The radiation loss of the designed transition circuit can also be significantly reduced.

In this paper, a tapered transition with narrow air cavities between SISPSL and GCPW is designed and optimized to achieve a smoother transition with broad bandwidth. Fig. 3 gives the electric field distribution of the core transition. From Fig. 3(a), it can be seen that the signal in SISPSL is balanced. To avoid the discontinuity of the transition, a tapered structure is designed with the gradually narrowing G5 signal line and widening G6 signal line. As shown in Fig. 3(a), the two lines of SISPSL are located on G5 and G6. As shown in Fig. 3(b), the signal line of MS is distributed on G5, and the ground of MS is distributed on G6. Besides, the width of stripline is close to the width of the signal trace of GCPW, as shown in Fig. 3(c) and Fig. 3(d). The ground planes of G6 for MS, stripline, and GCPW are the same, which ensures characteristics of good EM field matching.

In order to realize impedance matching, the characteristic impedance of each part is designed to be 50  $\Omega$ . The length of each air cavity is 2.86 mm and the width of each cavity is 1 mm. The radius of via holes Rvia is 0.15 mm. The width W1 of SISPSL is 0.53mm and the width W2 of MS is 0.47 mm. The width W3 of stripline is 0.33 mm, and the width W4 of GCPW is 0.48 mm. The length L1 of SISPSL is 1.2 mm. The length L2 of MS is 0.83 mm. The length L3 of stripline is 1 mm.

Table 1. Measurement performance comparisons of the transitions

| Reference | Туре              | Self-<br>packaging | Insertion Loss<br>(dB)                                                    | Return Loss<br>(dB) | Operating Bandwidth<br>(GHz) | Core Circuit Size (mm×mm) |

|-----------|-------------------|--------------------|---------------------------------------------------------------------------|---------------------|------------------------------|---------------------------|

| [5]       | DSPSL to MS       | No                 | <4.7#                                                                     | >10                 | 1-30                         | 28×16 <sup>#</sup>        |

| [6]       | DSPSL to MS       | No                 | <1.4                                                                      | >10                 | 1.3-9                        | 36×22#                    |

| [8]       | DSPSL to RWG      | No                 | <0.5                                                                      | >15                 | 31-39                        | 30×15#                    |

| This work | SISPSL to<br>GCPW | Yes                | <1.3 (DC to 10 GHz)<br><3.3 (10 GHz to 30 GHz)<br><8.9 (30 GHz to 60 GHz) | >10                 | DC-60                        | 17×15                     |

All of the compared loss are measured results.

<sup>\*:</sup> These data are estimated since the specific data are not given in the reference. RWG: Rectangular waveguide.

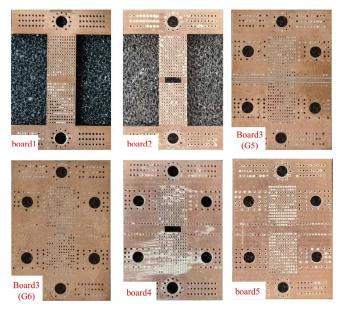

Fig. 4. Photographs of the fabricated back-to-back transition.

Since the frequency of the transition is up to 60 GHz, it is critical to avoid the cavity mode. Hence, the width of the air cavity is reduced as much as possible to increase the resonant frequency.

# III. SIMULATION AND EXPERIMENT RESULT

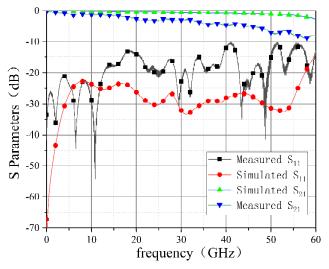

Based on the above methods, we designed an ultrawideband transition between SISPSL and GCPW, and it is fabricated by using the standard PCB technique. Copper is selected as the metal layer with a thickness of 0.018 mm. The simulations have been performed using EM simulation software and the measurements have been carried out utilizing a Vector Network Analyzer on a broad frequency band from DC to 60 GHz.

The fabricated self-packaged back-to-back ultrawideband transition and the simulated and measured results are shown in Fig. 4 and Fig. 5 respectively. The area of the core circuit is about 17 mm  $\times$  15 mm. The size of the whole test structure is less than 50 mm  $\times$  24 mm. The measured return loss is better than 10 dB from DC to 60 GHz. The measured insertion loss

Fig. 5. Simulated and measured results of the back-to-back transition.

including the losses from connectors is smaller than 1.3 dB from DC to 10 GHz, smaller than 3.3 dB from 10 GHz to 30 GHz, and smaller than 8.9 dB from 30 GHz to 60 GHz. There is a discrepancy between simulated and measured results, which is mainly due to the additional losses and phase shifts of coaxial cables and connectors, as well as the fabrication errors. Table 1 summarizes the performance comparisons of the transitions based on parallel strip lines. As compared with other transitions, the proposed transition in this paper has the advantages of broadband, compact, self-packaging, and low loss.

## IV. CONCLUSION

In this paper, a new ultrawideband transition between SISPSL and GCPW is designed for the first time. By achieving impedance matching and EM field matching, the obtained operating bandwidth of this transition achieves DC to 60 GHz. The proposed transition inherits the self-packaging feature, and it is convenient to realize high integration between SISPSL and other PCB circuits while reducing the overall circuit size at the same time. This work can be applied in the testing of wideband applications based on the SISPSL platform.

## ACKNOWLEDGMENT

This work was supported in part by the National Natural Science Foundation of China under Grant 62101381, the Young Elite Scientists Sponsorship Program by CAST under Grant 2021QNRC001, and in part by the National Natural Science Foundation of China for Key Project under Grant 61831017.

### REFERENCES

- [1] Q. Xue, "Double Side Parallel Strip Line and its Applications," in 2008 IEEE MTT-S International Microwave Workshop Series on Art of Miniaturizing RF and Microwave Passive Components, Chengdu, China, Dec. 2008, pp. 55–58.

- [2] Sheng Sun and Lei Zhu, "Stopband-enhanced and size-miniaturized low-pass filters using high-impedance property of offset finite-ground microstrip line," *IEEE Trans. Microwave Theory Techn.*, vol. 53, no. 9, pp. 2844–2850, Sep. 2005.

- [3] J.-X. Chen, C.-H. K. Chin, and Q. Xue, "Double-Sided Parallel-Strip Line With an Inserted Conductor Plane and Its Applications," *IEEE Trans. Microwave Theory Techn.*, vol. 55, no. 9, pp. 1899–1904, Sep. 2007

- [4] J. Liu, Y. Wang, K. Ma, and W. An, "A Differential SISPSL Branch-Line Coupler with Common-Mode Suppression Using Compensated Stub," *IEEE Trans. Circuits Syst. II*, pp. 1–1, 2022.

- [5] S.-G. Kim and K. Chang, "Ultrawide-Band Transitions and New Microwave Components Using Double-Sided Parallel-Strip Lines," *IEEE Trans. Microwave Theory Techn.*, vol. 52, no. 9, pp. 2148–2152, Sep. 2004.

- [6] X. Y. Zhang, J.-X. Chen, and Q. Xue, "Broadband Transition Between Double-Sided Parallel-Strip Line and Coplanar Waveguide," *IEEE Microw. Wireless Compon. Lett.*, vol. 17, no. 2, pp. 103–105, Feb. 2007.

- [7] P. L. Carro and J. de Mingo, "Analysis and Synthesis of Double-Sided Parallel-Strip Transitions," *IEEE Trans. Microwave Theory Techn.*, vol. 58, no. 2, pp. 372–380, Feb. 2010.

- [8] Lei Xia, Ruimin Xu, and Bo Yan, "Wideband millimeter wave waveguide to double-sided parallel-strip line transition," in 2012 International Conference on Computational Problem-Solving (ICCP), Leshan, China, Oct. 2012, pp. 400–401.

- [9] K. Ma and K. T. Chan, "Quasi-planar Circuits with Air Cavities," PCT patent WO/2007/149046, Dec. 27, 2007.

- [10] K. Ma, N. Yan, and Y. Wang, "Recent Progress in SISL Circuits and Systems: Review of Passive and Active Circuits Demonstrating SISL's Low Loss and Self-Packaging and Showcasing the Merits of Metallic, Shielded, Suspended Lines," *IEEE Microwave*, vol. 22, no. 4, pp. 49–71, Apr. 2021.