#### Tu01D-4

## A 74.8-88.8 GHz Wideband CMOS LNA Achieving +4.73 dBm OP1dB and 6.39 dB Minimum NF

Linfeng Zou<sup>1</sup>, Kangjie Zhao<sup>1</sup>, Zonghua Fang<sup>1</sup>, Leilei Huang<sup>1</sup>, Boxiao Liu<sup>1</sup>, Chunqi Shi<sup>1</sup>, Guangsheng Chen<sup>2</sup>, Jinghong Chen<sup>3</sup>, Runxi Zhang<sup>1</sup>

<sup>1</sup>IMCS, East China Normal University, Shanghai, China <sup>2</sup>Shanghai Eastsoft Microelectronics Co. Ltd., Shanghai, China <sup>3</sup>ECE, University of Houston, Houston, USA

### Outline

- Motivation and Challenges

- Wideband LNA in 55nm CMOS

Measurement Results

#### **Motivation**

- Broadband mmWave transceivers are needed to support 5G and beyond high data-rate wireless communication and high-resolution wireless sensing applications

- Nanoscale CMOS is attractive offering high integration density, cost-efficient and high-yield solutions

- LNA plays an important role in defining the receiver noise figure (NF) and bandwidth (BW)

### IMS Challenges and Proposed Solutions

- Challenging to simultaneously achieve NF, BW, linearity and area efficiency

- Wide bandwidth is achieved at the expense of a large die area and severe passive network loss

- Transmitter leakage and isolation between antennas degrade linearity

- Broadband input matching limits the noise performance

- Proposed solutions

- Hybrid broadband inter-stage network for wide BW

- Inductor-feedback common-gate-shorting for high gain and high OP1dB

- Out-of-phase-dual-coupling for low noise and high gain

### **Outline**

Motivation and Challenges

Wideband LNA in 55nm CMOS

Measurement Results

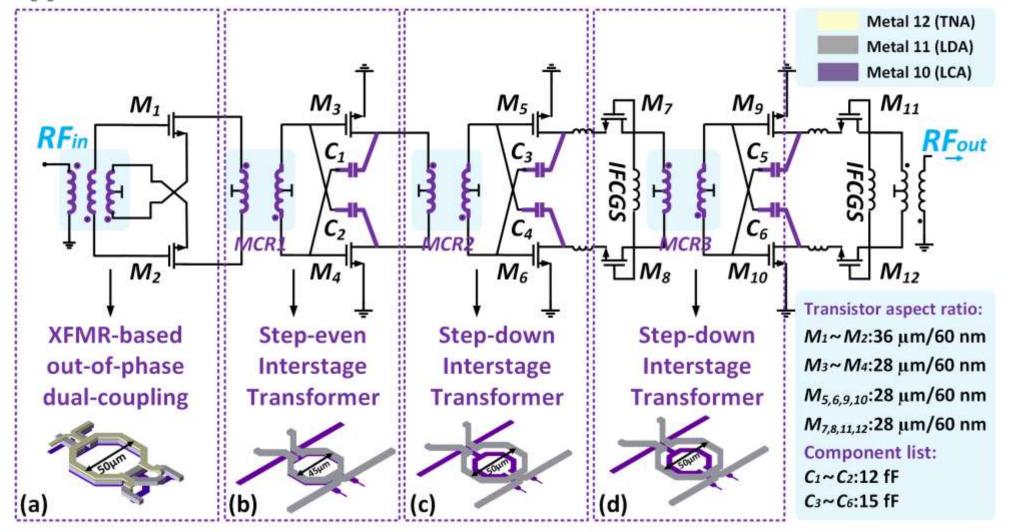

#### 74.8-88.8 GHz CMOS LNA

4 stage: 1 CG+1 CS+2 Cascode, differential topology, single-ended input and output

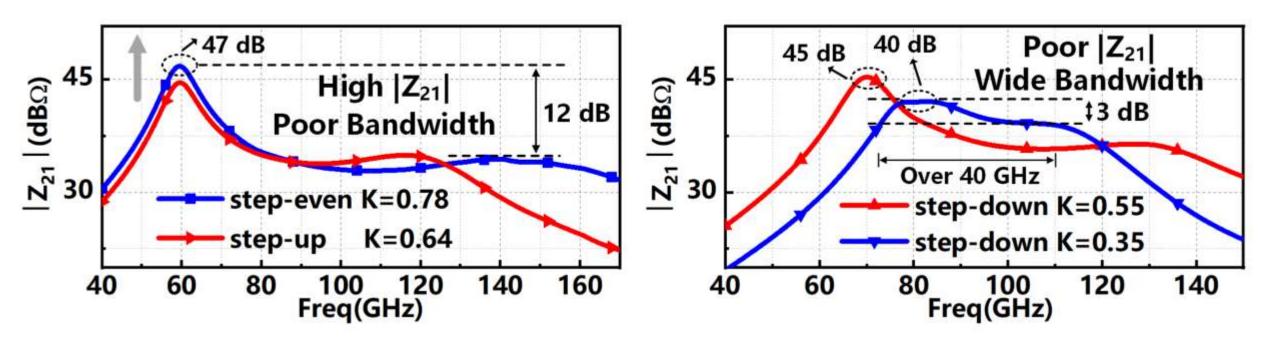

# Hybrid Broadband Interstage Network (HBIN) for Wide Bandwidth

(a)  $|Z_{21}|$  of step-even/up transformer

(b)  $|Z_{21}|$  of step-down transformer

#### Simulation Results of HBIN

(a)  $|Z_{21}|$  of Interstage Coupling network (b) Comparison of Overall  $S_{21}$  and  $|Z_{21}|$

# Connecting Minds. Exchanging Ideas.

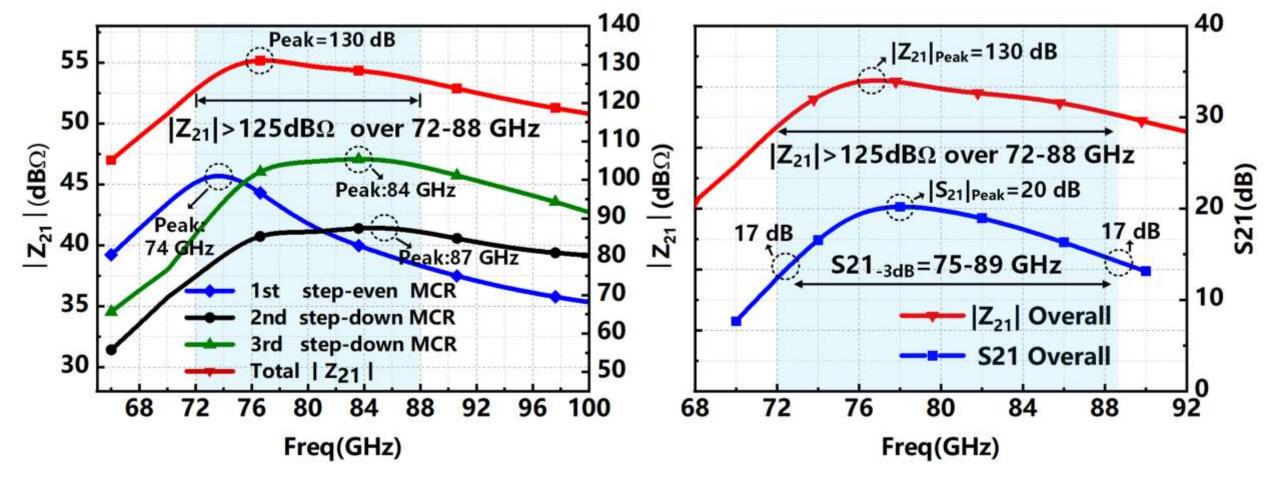

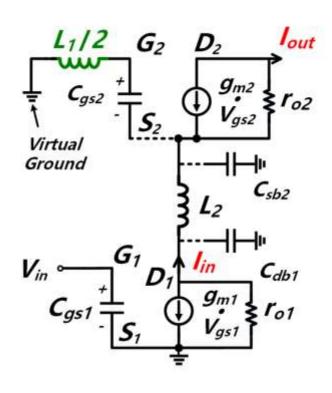

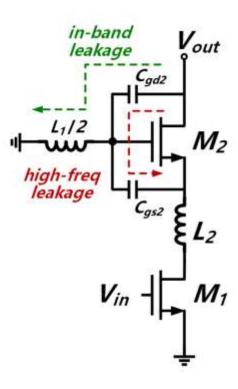

### IMS Inductor-Feedback Common-Gate-Shorting

### (IFCGS) for High Gain and High OP1dB

(a) IFCGS circuit

- (b) Equivalent circuit

- (c) Leakage analysis

$$I_{out} \approx I_{in} \cdot rac{g_m}{\left\{g_m + s \left[C_{sb2}\left(1 - \omega^2 rac{L_1}{2}C_{gs2}\right) + C_{gs2}\right]\right\}}$$

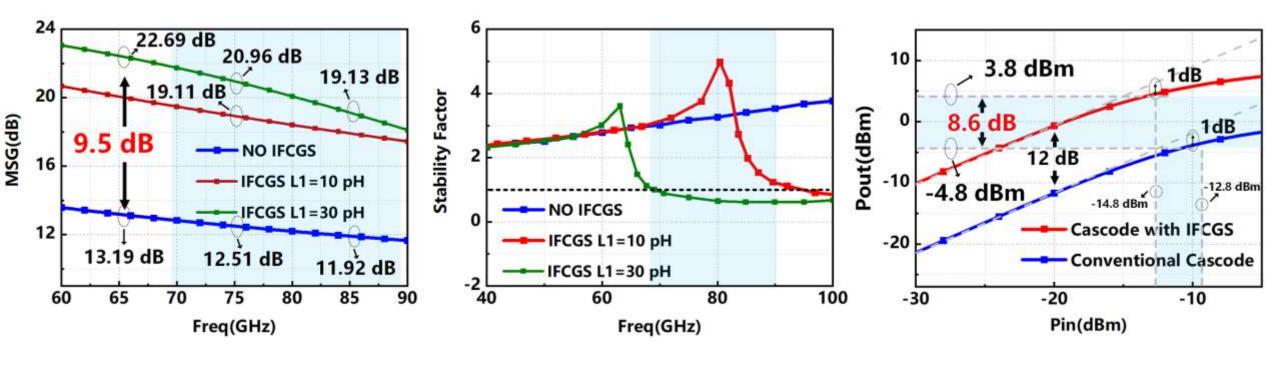

### Simulation Results of IFCGS

L1=10 pH, MSG improved by 9.5 dB, OP1dB improved by 8.6 dB

(b) Stability simulation

(a) MSG simulation

(c) OP1dB simulation

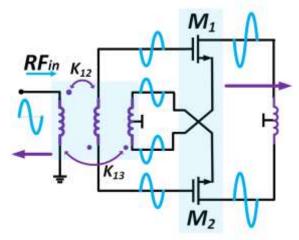

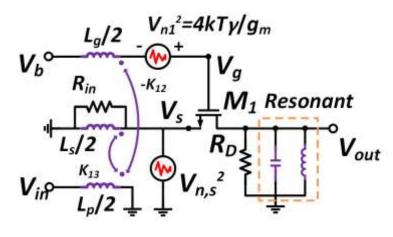

### Out-of-Phase-Dual-Coupling (OPDC) for Low Noise and High Gain

(a) OPDC CG circuit

(c) Equivalent circuit

(b) Input balun

voltage gain:

$$\frac{V_{out}}{V_{in}} = (n_g K_{12} + n_s K_{13}) g_m R_D$$

$$NF = 1 + \frac{\gamma}{(n_q K_{12} + n_s K_{13})}$$

$$+\frac{4}{(n_g K_{12}+n_s K_{13})g_m R_D}$$

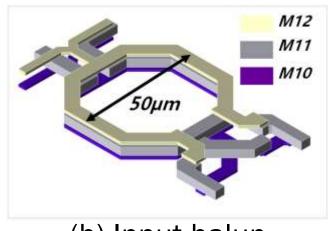

#### Simulation Results of OPDC

CASE1:  $K_{12}=0.65 K_{13}=0.67 L_g=129 pH L_s=180 pH$

CASE2:  $K_{12}=0.73 K_{13}=0.74 L_q=129 pH L_s=136 pH$

CASE1:  $K_{12}=0.65 K_{13}=0.67 L_g=129pH L_s=180pH$  CASE2:  $K_{12}=0.73 K_{13}=0.74 L_g=129pH L_s=136pH$

In CASE2, MSG improved by 6 dB, NF decreased by 0.7 dB

### **Outline**

Motivation and Challenges

Wideband LNA in 55nm CMOS

Measurement Results

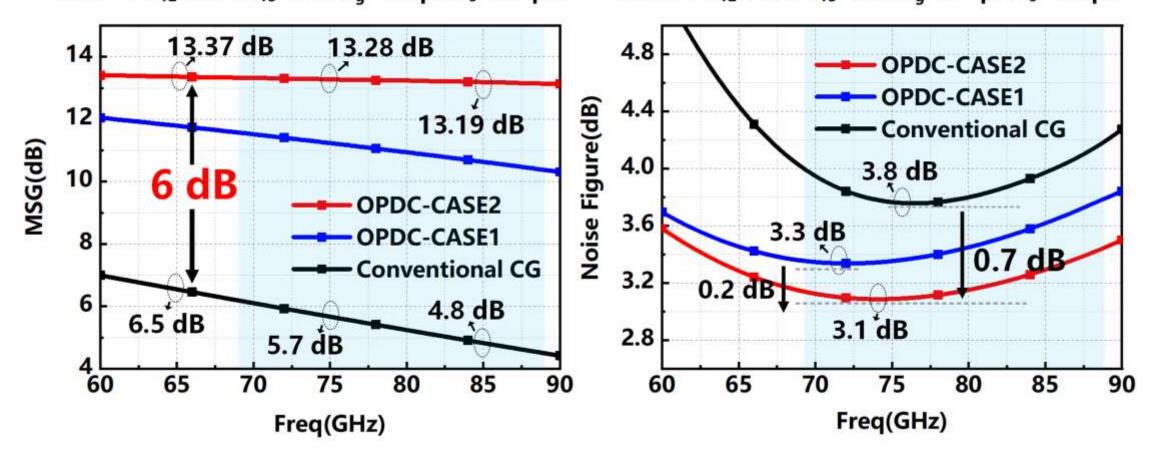

### Die Photo of the Proposed LNA

Process: 55-nm CMOS, Area: 895\*120µm<sup>2</sup>

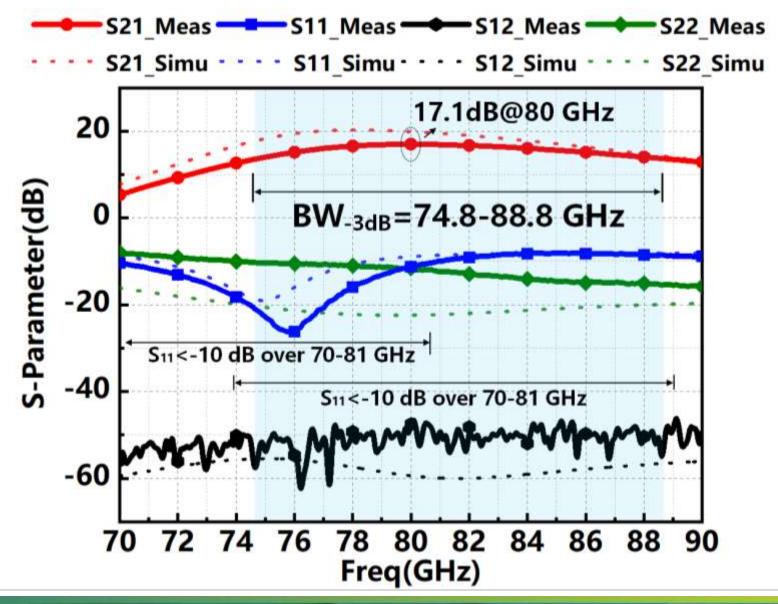

### MS Simulated and Measured S-parameters

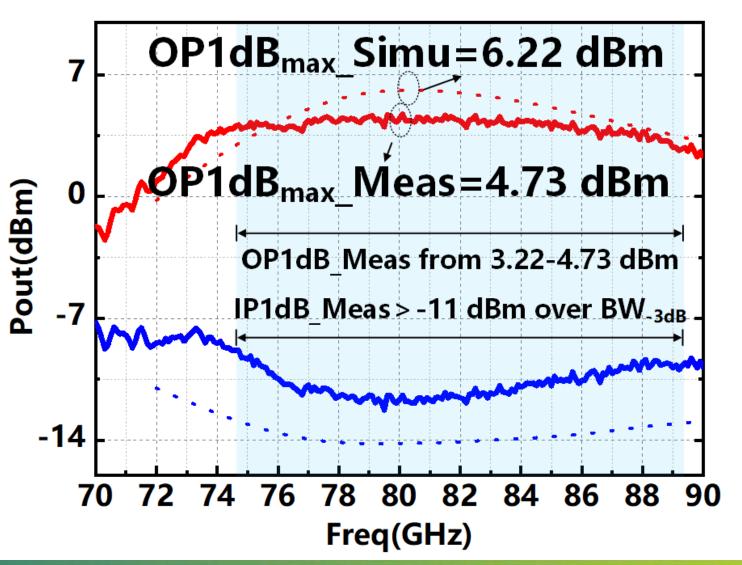

### Large Signal Measurement Results

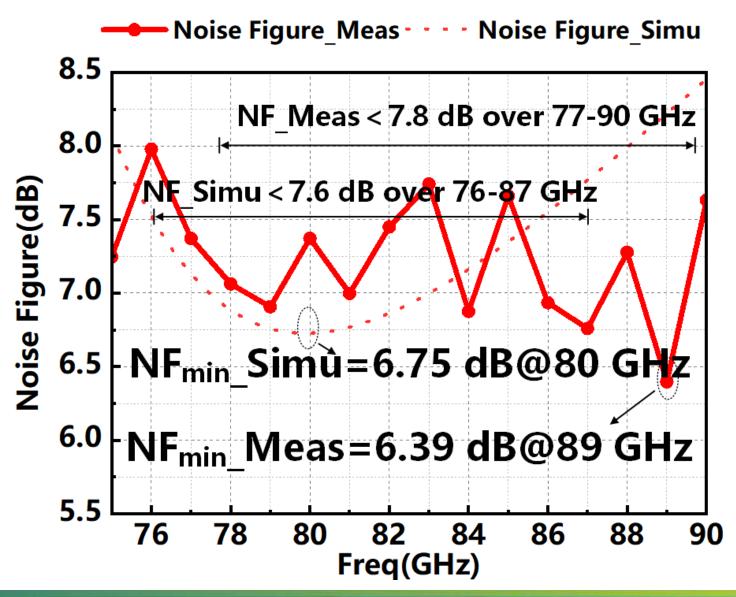

### NF Measurement Results

### **Performance Comparison**

| Ref                     | [10] JSSC<br>2017        | [11] TMTT<br>2020 | [12] RFIC<br>2020 | [8] IMS<br>2020            | [13] MWCL<br>2022   | This Work                                |

|-------------------------|--------------------------|-------------------|-------------------|----------------------------|---------------------|------------------------------------------|

| Technology              | 28nm CMOS                | 22nm FDS0I        | 65nm CMOS         | 55nm CMOS                  | 40nm CMOS           | 55nm CMOS                                |

| Topology                | 1-stage CG<br>4-stage CS | 3-stage CSCG      | 3-stage CS        | 2-stage CS<br>1-stage CSCG | 3-stage CS          | 1-stage CG<br>1-stage CS<br>2-stage CSCG |

| Structure               | Differential             | Single-ended      | Differential      | Differential               | Differential        | Differential                             |

| Peak Gain(dB)           | 29.6                     | 24                | 25                | 15                         | 19                  | 17.1                                     |

| BW <sub>3dB</sub> (GHz) | 28.3<br>(68.1-96.4)      | 13<br>(70.5-83.5) | 7.5<br>(53.5-61)  | 7.6<br>(78.9-86.5)         | 16.1<br>(76.5-92.6) | 14<br>(74.8-88.8)                        |

| Minimum NF(dB)          | 6.4                      | 4.6               | 4.8               | 5                          | 5.7                 | 6.39                                     |

| IP1dB(dBm)              | -28.1                    | -26.8             | -22               | -13.2                      | -19                 | -12.37                                   |

| OP1dB(dBm)              | +1.5                     | -2.8#             | +3.0#             | +1.8#                      | O#                  | +4.73                                    |

| P <sub>DC</sub> (mW)    | 31.3                     | 16                | 47                | 72.7                       | 23.4                | 72.4                                     |

| Area(mm²)               | 0.675                    | 0.35              | 0.26              | 0.08                       | 0.17                | 0.107*                                   |

| FOM₁                    | 12.57                    | 14.28             | 8.86              | 13.01                      | 26.84               | 24.29                                    |

<sup>#</sup> Estimated values

$FOM_1 = Gain[lin] \cdot BW_{-3dB}[MHz] \cdot IP1dB[lin]/\{P_{dc}[mW] \cdot (F-1)\}$

<sup>\*</sup> Area excluding bondpads

### **Outline**

Motivation and Challenges

Wideband LNA in 55nm CMOS

Measurement Results

- Hybrid step-even and step-down interstage coupling network to achieve high bandwidth

- Inductor-Feedback Common-Gate-Shorting to simultaneously obtain high gain and high OP1dB

- Out-of-Phase-Dual-Coupling to achieve high gain and low noise

- Measurement results of the 55nm CMOS LNA demonstrated a -3dB bandwidth of 14 GHz, a 17.1 dB peak gain, a minimum NF of 6.39 dB, and 4.73 dBm OP1dB

# Thank you!

Q&A