#### **Tu1E-4**

## V-Band LC-VCO and Doubler with Wide Tuning Range and Low Phase Noise Using Series-Shunt Anti-Parallel SiGe HBT Switches

Wonsub Lim<sup>1</sup>, Arya Moradinia<sup>1</sup>, Sanghoon Lee<sup>1</sup>, Clifford D. Cheon<sup>1</sup>, Christopher T. Coen<sup>2</sup>, Nelson E. Lourenco<sup>2</sup>, and John D. Cressler<sup>1</sup>

<sup>1</sup>Georgia Tech, Atlanta, USA

<sup>2</sup>Advanced Concepts Laboratory, Georgia Tech Research Institute, Atlanta, USA

#### **Outline**

- Motivation and Problem Statement

- Proposed SSAP Capacitor Bank

- VCO Implementation

- Measurement Results

- Summary

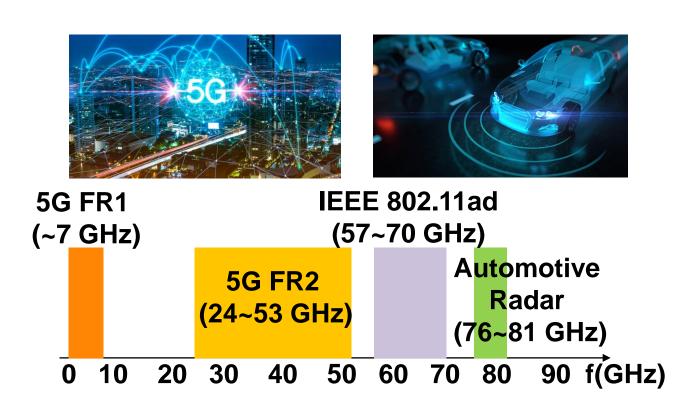

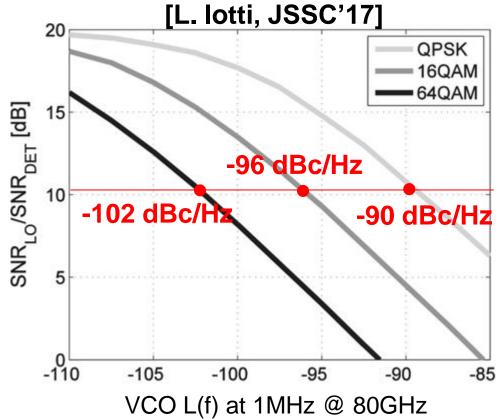

## Phase Noise Challenges at Mm-wave

Mobile communication and radar systems require wide bandwidth and low phase noise

## Connecting Minds. Exchanging Ideas. Tuning Range Challenges at Mm-wave

Tuning range decreases as frequency increases

$$f_{osc} = \frac{1}{2\pi\sqrt{L_T(C_{var} + C_b + C_{fix})}}$$

[W. Wang, BCICTS'19]

| Frequency       | 10 GHz | 20 GHz | 40 GHz |  |  |

|-----------------|--------|--------|--------|--|--|

| Inductance (pH) | 438    | 295    | 182    |  |  |

| madetance (pm)  |        |        |        |  |  |

### **Limitations for Prior Designs**

[H. Jia, ISSCC'21]

Low phase noise

Narrow tuning range

[Z. Zong, JSSC'16]

High phase noise

Wide tuning range

- Transformer-coupled QVCO has low PN but narrow FTR

- Magnetically tuned VCO has wide FTR but high phase noise

- How to improve both PN and FTR?

### Outline

- Motivation and Problem Statement

- Proposed SSAP Capacitor Bank

- VCO Implementation

- Measurement Results

- Summary

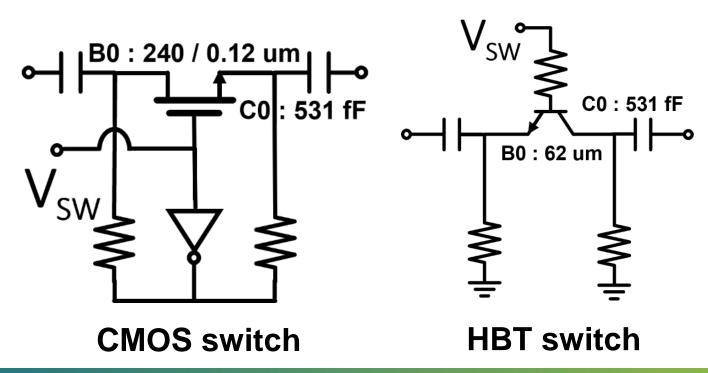

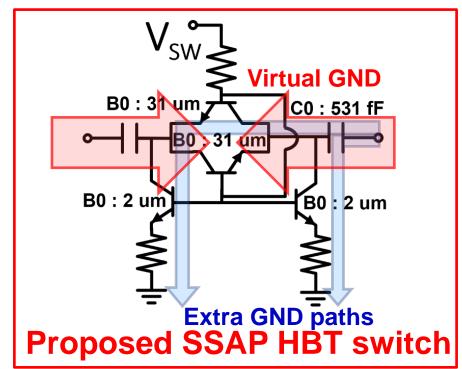

### Proposed SSAP SiGe HBT Switch

- Series-Shunt Anti-Parallel (SSAP) SiGe HBT switch uses a series-shunt switch topology in an anti-parallel fashion

- Low series R<sub>on</sub>, high shunt R<sub>off</sub>, and low parasitic capacitance

# IMS Switched Capacitor Bank Comparison Someoning Minds. Exchanging Ideas.

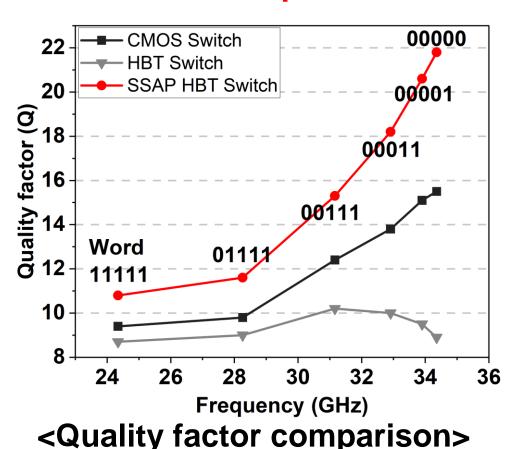

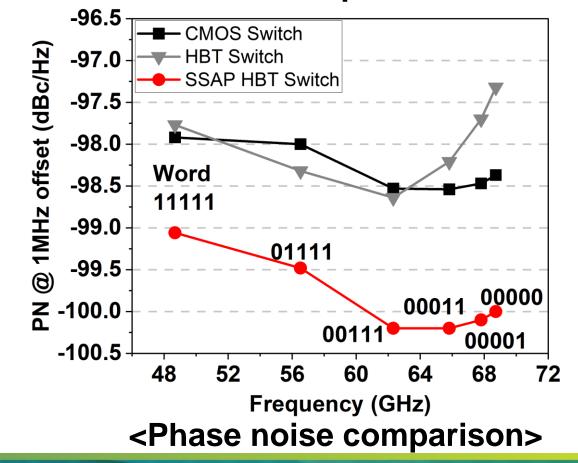

The proposed SSAP capacitor bank shows 29% higher Q and 1.5 dB PN improvement compared to the CMOS pair

### Outline

- Motivation and Problem Statement

- Proposed SSAP Capacitor Bank

- VCO Implementation

- Measurement Results

- Summary

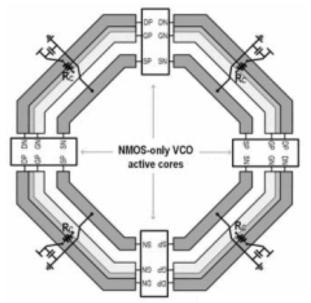

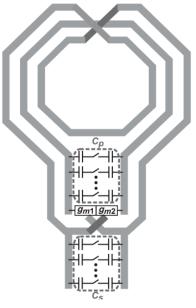

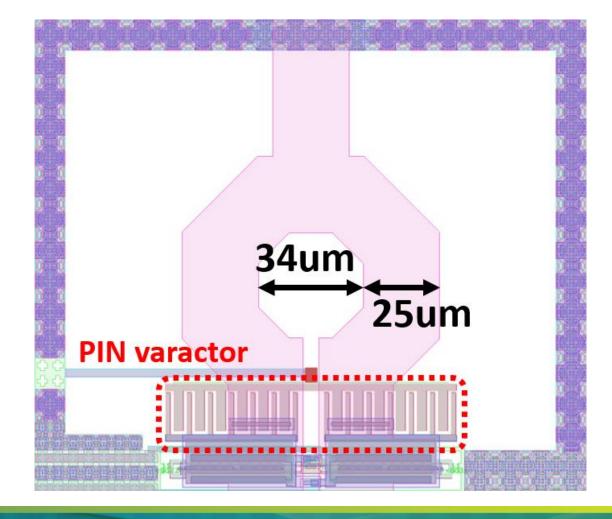

### Inductor and Varactor Layout

- 49.4 pH with Q of 27.6 at 30 GHz Inductor

- low PN and wide FTR

$$FTR = 2 \frac{\sqrt{\Delta C_{max} + C_{fix}} - \sqrt{C_{fix}}}{\sqrt{\Delta C_{max} + C_{fix}} + \sqrt{C_{fix}}}$$

$PN (\Delta w) \propto \frac{w^3 L}{A^2 Q}$

- A PIN-diode varactor

- $-146.7 \sim 200 \text{ fF at } 0V \sim 2.3V$

- linear voltage characteristics

- Minimized the length of the transmission lines

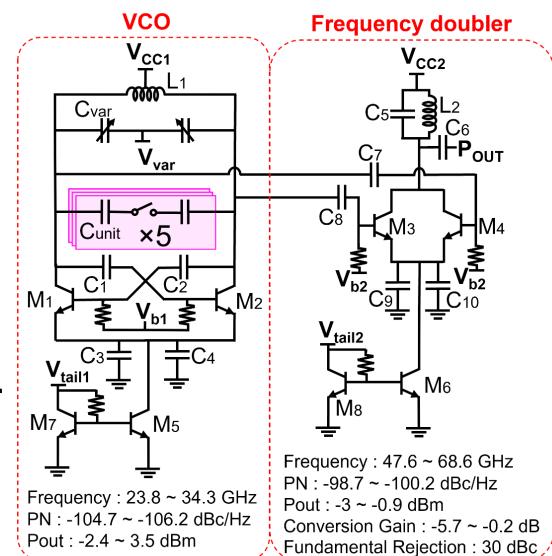

#### Schematic and Simulation Results

- 5-bit SSAP capacitor bank

- Class C type VCO

- Low PN

- Independent push-push doubler

- High Fundamental Rejection

| Component name                  | Value             |  |  |  |  |

|---------------------------------|-------------------|--|--|--|--|

| L <sub>1</sub>                  | 49.4 pH           |  |  |  |  |

| L <sub>2</sub>                  | 69 pH             |  |  |  |  |

| Cvar                            | 146.7 fF - 200 fF |  |  |  |  |

| Cunit                           | 25.4 fF           |  |  |  |  |

| C1, C2                          | 270 fF            |  |  |  |  |

| C <sub>3</sub> , C <sub>4</sub> | 450 fF            |  |  |  |  |

| <b>C</b> 5                      | 83 fF             |  |  |  |  |

| <b>C</b> <sub>6</sub>           | 357 fF            |  |  |  |  |

| C <sub>7</sub> , C <sub>8</sub> | 270 fF            |  |  |  |  |

| $C_{9}$ , $C_{10}$              | 405 fF            |  |  |  |  |

| $M_1 - M_6$                     | 16 µm             |  |  |  |  |

| M <sub>7</sub> , M <sub>8</sub> | 2.6 µm            |  |  |  |  |

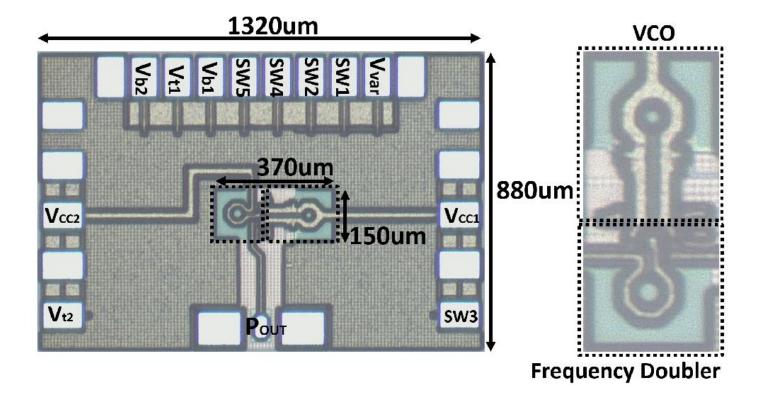

## Chip Micrograph of the VCO

- 130-nm GlobalFoundries 8XP SiGe BiCMOS process

- Compact die size : 370um × 150um = 0.055mm<sup>2</sup>

#### **Outline**

- Motivation and Problem Statement

- Proposed SSAP Capacitor Bank

- VCO Implementation

- Measurement Results

- Summary

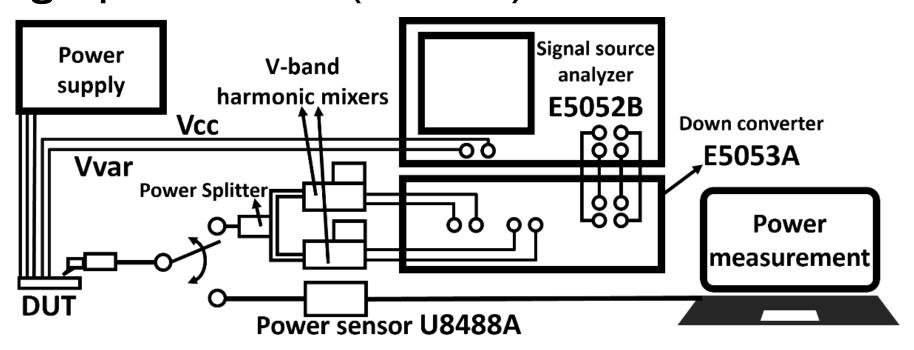

### Measurement Setup

- Keysight E5052B was used to measure operating frequency and the accurate phase noise

- The output power of the oscillator was measured with the Keysight power sensor (U8488A)

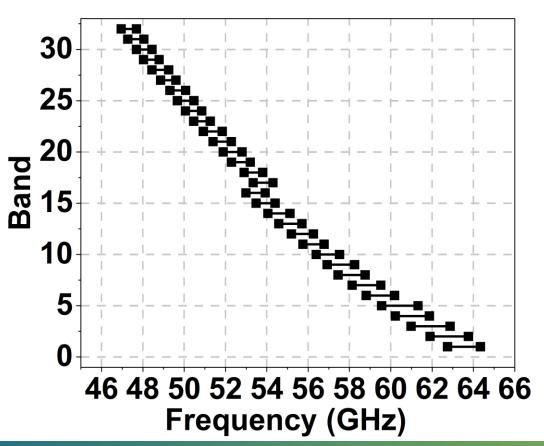

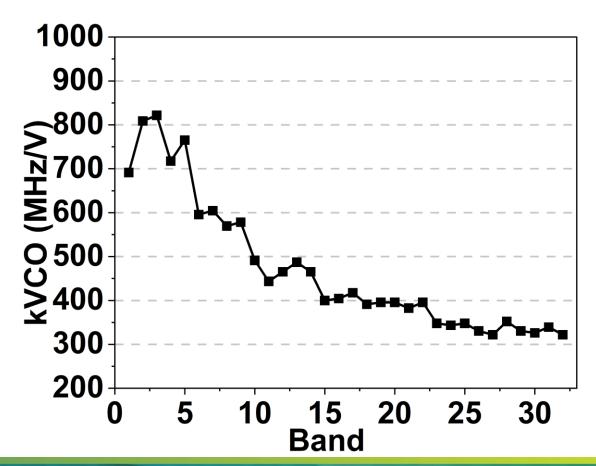

#### Measured FTR and kVCO

- Oscillation frequency covers 47 GHz to 64 GHz (FTR: 31%)

- kVCO is 470 MHz/V on average, with 820 MHz/V at maximum

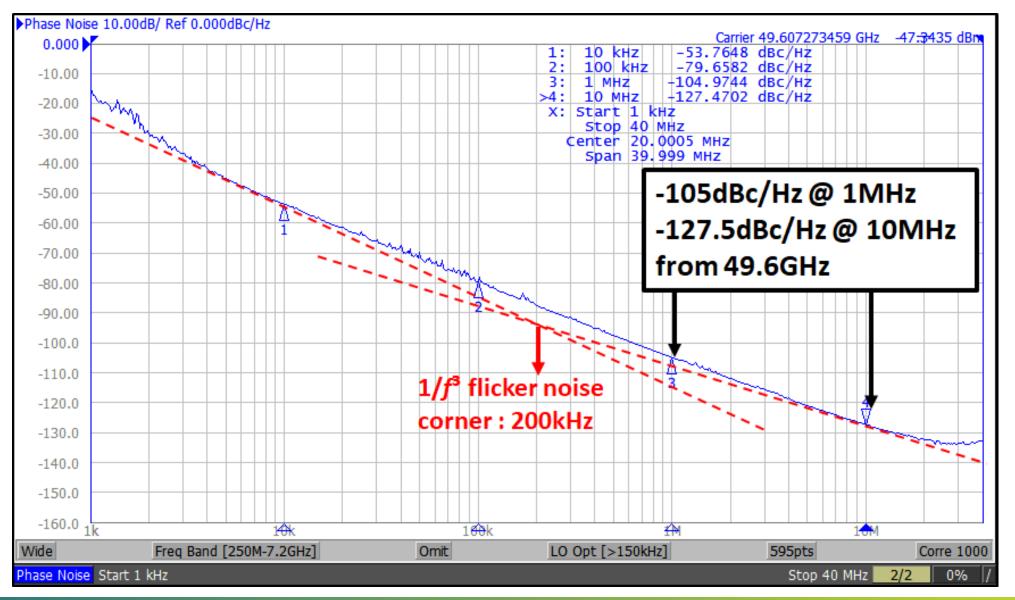

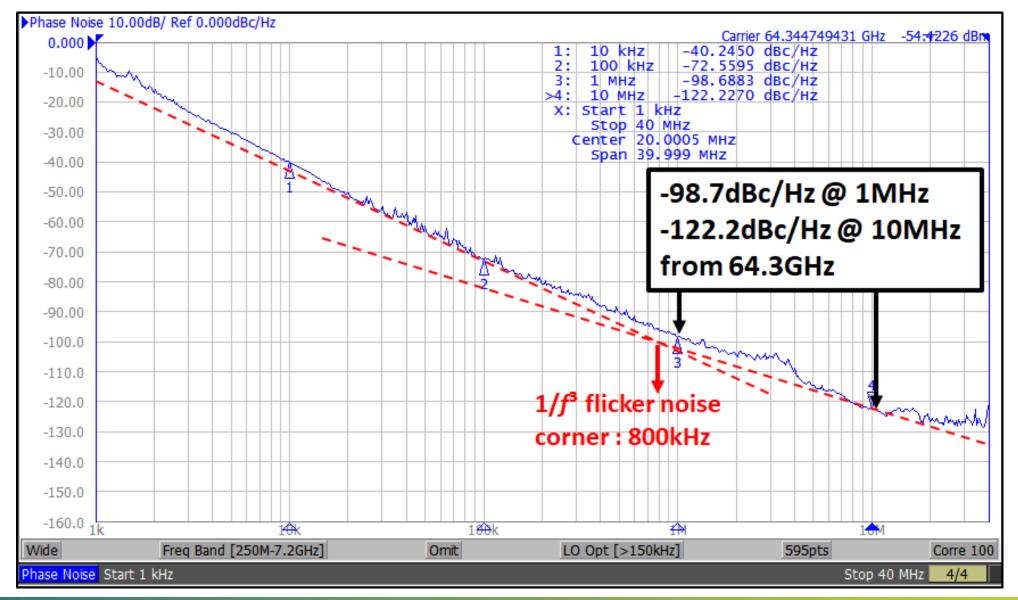

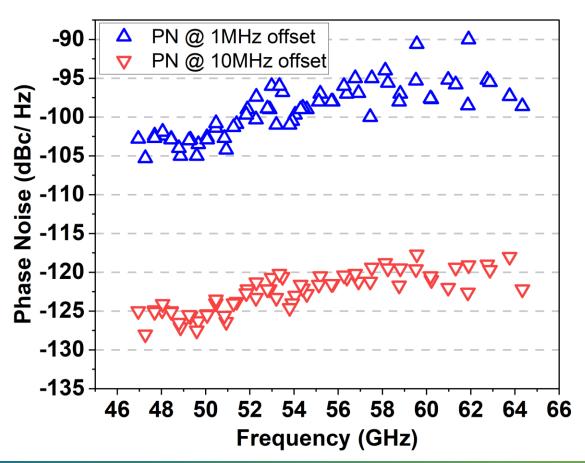

#### Measured Phase Noise

#### Measured Phase Noise

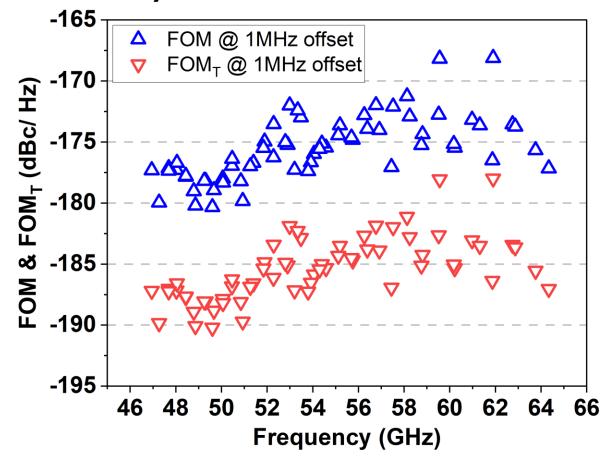

### Measured PN and FOM

- PN @ 1MHz: -95 to -105 dBc/Hz

- FOM @ 1MHz: -171.3 to -180.3 dBc/Hz

### **Comparison Table**

| Reference               | This Work   | JSSC' 22 [1] | TMTT' 16 [2]  | ISSCC' 21 [3] | TMTT' 15 [4]  | JSSC' 13 [5] | JSSC' 16 [6] | TMTT' 15 [7] |

|-------------------------|-------------|--------------|---------------|---------------|---------------|--------------|--------------|--------------|

| Neierence               | TIIIS VVOIR | JJJC ZZ [1]  | 110111 10 [2] | 13300 21 [3]  | 110111 13 [4] | 1336 13 [3]  | 1336 10[0]   | 110111 13[/] |

| Technology              | 130nm       | 28nm         | 95nm          | 65nm          | 65nm          | 65nm         | 40nm         | 65nm         |

|                         | SiGe        | CMOS         | CMOS          | CMOS          | CMOS          | CMOS         | CMOS         | CMOS         |

| Number of Cores         | 1           | 4            | 4             | 4             | 1             | 1            | 1            | 1            |

| Tuning Range (GHz)      | 47 to 64.3  | 55 to 62.8   | 51.7 to 56.6  | 52.4 to 60.4  | 55.1 to 70.4  | 57.5 to 90.1 | 48.4 to 62.5 | 47.6 to 71   |

|                         | (31.2%)     | (13.4%)      | (9.1%)        | (14.2%)       | (24.6%)       | (44.2%)      | (25.4%)      | (39.5%)      |

| Output Power (dBm)      | -7 to 0     | -5 to -1     | NA            | NA            | -15 to -10    | -20 to -25   | -14 to 6     | NA           |

| Power consumption (mW)  | 58 to 78    | 15.3         | 24            | 22.5 to 23.6  | 21.5          | 8.4 to 10.8  | 10.5         | 8.9 to 10.4  |

| PN @ 1MHz (dBc/Hz)**    | -105        | -95          | -95.5         | -104.7        | -92.2         | -86*         | -100.1       | -92*         |

| PN @ 10MHz (dBc/Hz)**   | -127.5      | -121.7       | -119.2        | -130*         | -115          | -112.2       | -122.3       | -113.4       |

| FOM @ 1MHz (dBc/Hz)**   | -180.3      | -178         | -176.7        | -186.5        | -174.9        | -173.9*      | -181.5       | -176*        |

| FOM @ 10MHz (dBc/Hz)**  | -182.8      | -184.7       | -180.4        | -191.8        | -177.7        | -180         | -183.7       | -179         |

| FOM⊤ @ 1MHz (dBc/Hz)**  | -190.2      | -180.7       | -175.9        | -189.6        | -182.7        | -186.8*      | -189.6       | -187.8*      |

| FOM⊤ @ 10MHz (dBc/Hz)** | -192.7      | -187.4       | -179.6        | -194.9*       | -185.5        | -192.2       | -191.8       | -190.3       |

$$FOM = PN\left(\Delta f\right) + 10\log\left(\frac{P_{DC}}{1mW}\right) - 20\log\left(\frac{f_{osc}}{\Delta f}\right), FOM_T = FOM - 20\log\left(\frac{FTR(\%)}{10\%}\right)$$

<sup>\*</sup> estimated from the Figure; \*\* Reporting best-case for each publication

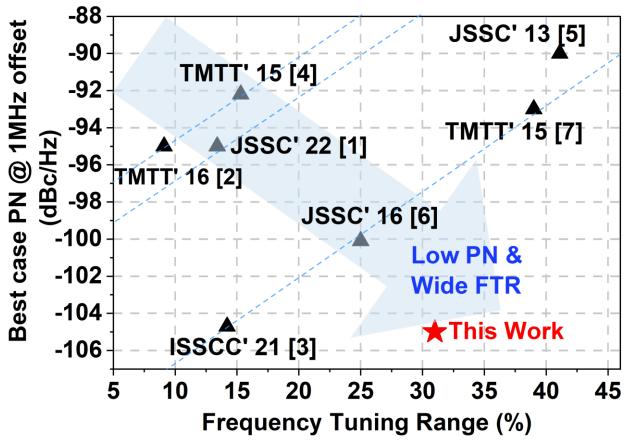

### PN and FTR Comparison

Proposed VCO achieved both low PN and wide FTR

<Comparison of PN and FTR with recent 50–63GHz state-of-the-art VCOs>

### Summary

- The first VCO using the novel Series-Shunt Anti-Parallel SiGe HBT Switches

- Symmetric structure

- 29% higher Q than CMOS pair

- Achieved wide FTR of 31% and low PN of -105 dBc/Hz at 1 MHz offset at 50 GHz

- FOM<sub>T</sub> of -190.2 dBc/Hz at 1MHz offset

- An attractive candidate topology for V-band VCO applications