#### **We1C-2**

# A 1.5-to-17GHz Non-uniform Distributed Power Amplifier Using Reconfigurable Modules in 0.25µm GaN HEMT

Shijie Chen<sup>1</sup>, Fuchen Yan<sup>1</sup>, Yuan Liang<sup>2</sup>, Shu Ma<sup>1</sup>, Dexin Shi<sup>1</sup>, Xiang Li<sup>3</sup>, Huaizong Shao<sup>1</sup>, Tao Yang<sup>1</sup> and Yong Wang<sup>1</sup>

<sup>1</sup>University of Electronic Science and Technology of China, Chengdu, China

<sup>2</sup>Guangzhou University, Guangzhou, China

<sup>3</sup>Nanhu Laboratory, Jiaxing, China

- High Efficency NDPA Design Challenges

- PCPCT Design Details

- FRDPA Design Details

- Demonstration of GaN-based FRDPA

- Conclusion

- High Efficency NDPA Design Challenges

- PCPCT Design Details

- FRDPA Design Details

- Demonstration of GaN-based FRDPA

- Conclusion

## High PAE NDPA Design Challenges

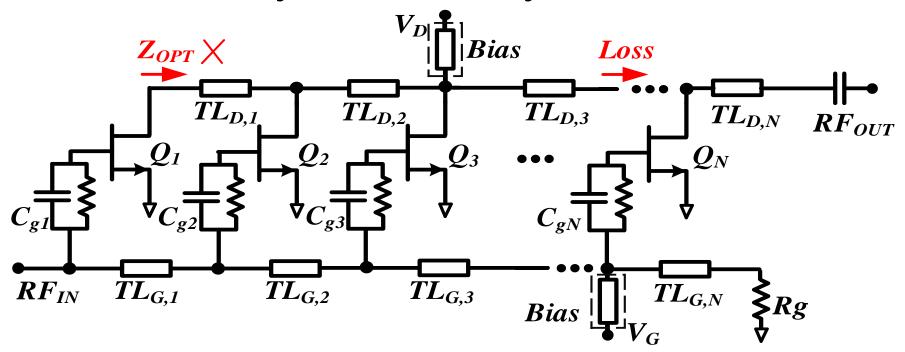

- The reason of Non-Uniform Distributed's (NDPA) low PAE:

- The impedance mismatch of transistors

- —The loss of output match network

- The non-ideality of bias circuitry

## High PAE NDPA Design Challenges

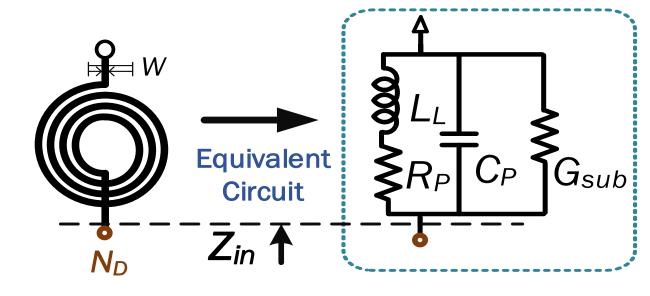

- The characteristic of the ideal on-chip bias circuitry:

- -Higher impedance  $\rightarrow$  larger inductance  $L_L$

- -Higher self-resonance point  $\rightarrow$  Smaller parasitic capacitance  $C_P$

- -More sufficient current carrying → wider transmission lines W

## It is difficult to achieve!

#### **Drain Bias Inductor**

## High PAE NDPA Design Challenges

- The effect of the non-ideal bias circuitry on NDPA:

- -Exhibiting poor choke effect over a wide bandwidth.

- -Resulting in a bandpass effect.

- High Efficency NDPA Design Challenges

- PCPCT Design Details

- FRDPA Design Details

- Demonstration of GaN-based FRDPA

- Conclusion

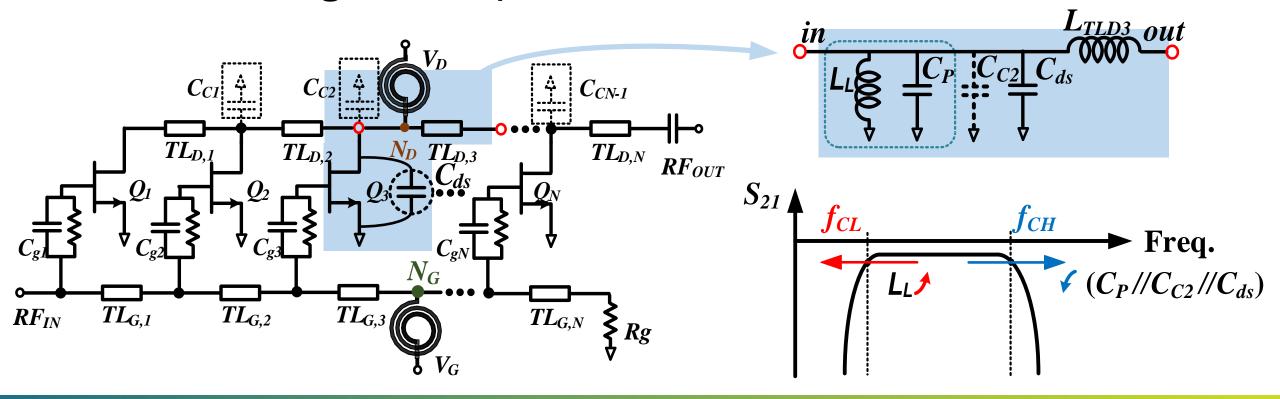

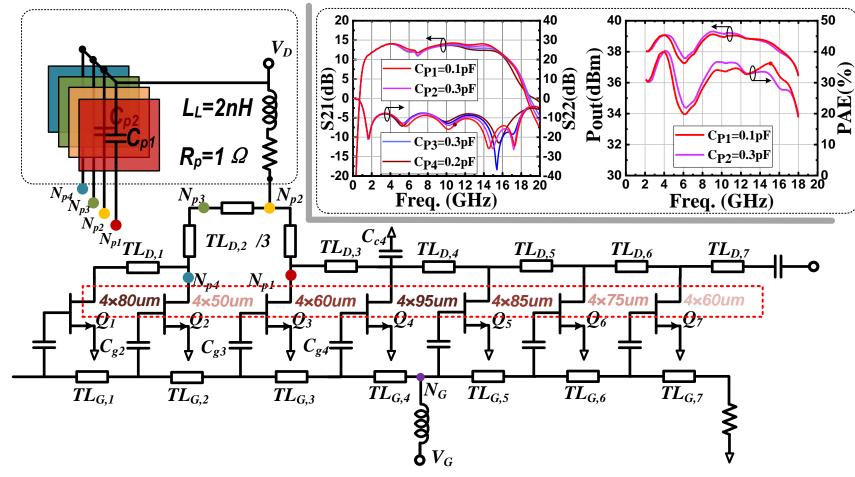

## **PCPCT Design Details**

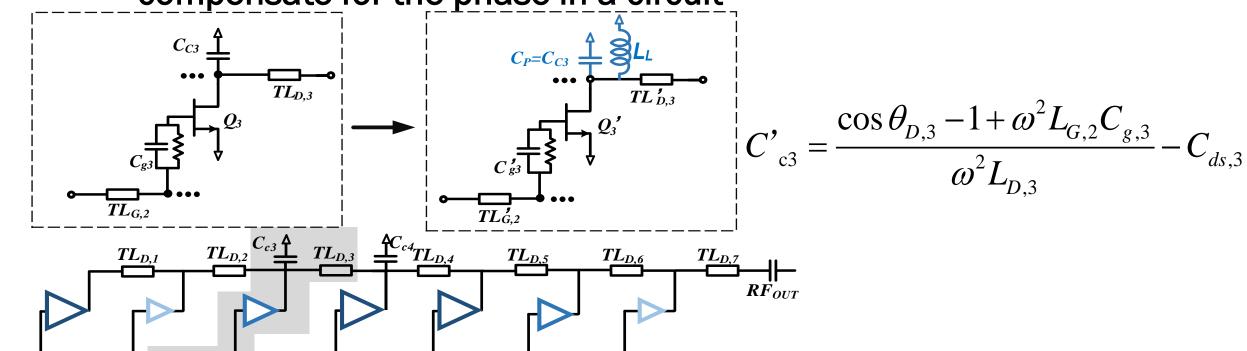

- Parasitic capacitance phase compensation technique(PCPCT)

- -Utilizing the parasitic capacitance of a bias inductor to

$TL_{G,4}$

$RF_{IN}$

$TL_{G.1}$

$TL_{G.3}$

$TL_{G,2}$

$\overline{TL_{G,6}}$

$\overline{TL_{G,5}}$

$\overline{TL_{G,7}}$

## **PCPCT Design Details**

• A simulation of  $S_{22}$ , PAE and  $P_{\rm sat}$  for different  $C_{\rm pi\,(i=1,2)}$  are

nearly identical

- High Efficency NDPA Design Challenges

- PCPCT Design Details

- FRDPA Design Details

- Demonstration of GaN-based FRDPA

- Conclusion

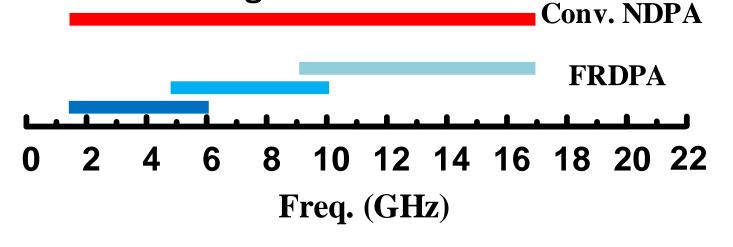

- Frequency Reconfigurable Distributed PA(FRDPA) Design

- Frequency reconfigurable application scenarios

- For multi-bandwidth PAs, the instantaneous operating bandwidth do not need to be so wide.

- FRDPA has the potential to replace conventional NDPA if the switching speed is fast enough.

Bandwidth narrowed, performance improved!

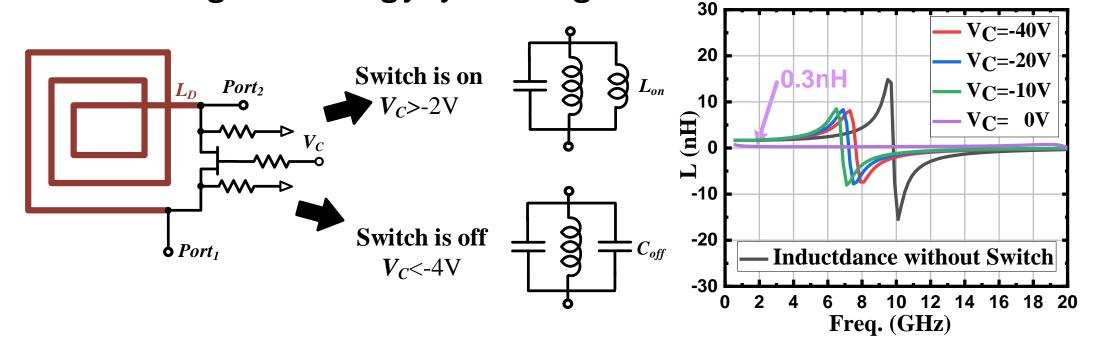

- Frequency Reconfigurable Distributed PA(FRDPA) Design

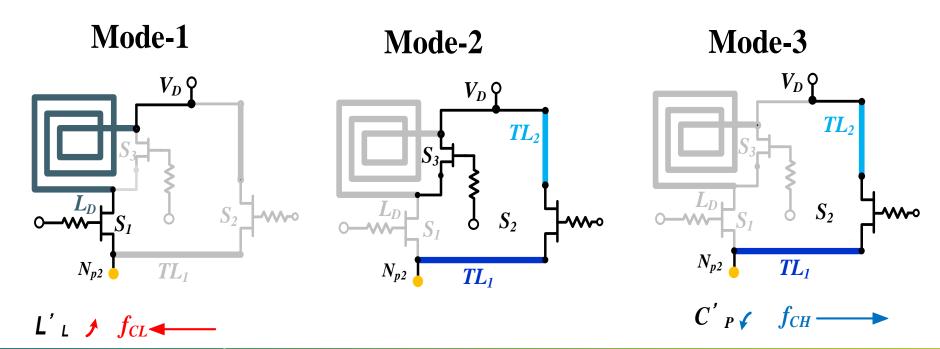

- Reconfigurable Drain Bias Choke Module

- The self-resonant point and inductance of the square inductor needs to be changed accordingly by switching

- Reconfigurable Drain Bias Choke Module

- Mode 1 provides a larger inductance L'

at low frequencies.

- Mode 2 provides the better load impedance for transistors.

- Mode 3 provides a smaller capacitance C'<sub>P</sub> at high frequencies.

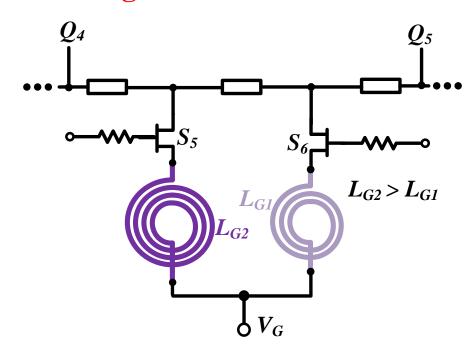

- Reconfigurable Gate Bias Choke Module and dumping load module

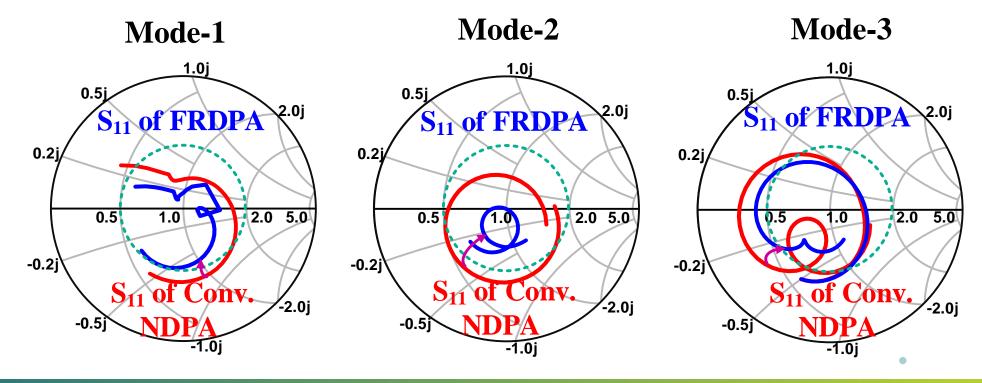

- These two rec. module can optimize S<sub>11</sub> and optimize source impedance of transistors.

#### **Reconfigurable Gate Bias Module**

#### **Mode Control Table**

| Mode        | Gate Control<br>Voltage |           |           |  |

|-------------|-------------------------|-----------|-----------|--|

|             | <b>S5</b>               | <b>S6</b> | <b>S7</b> |  |

| 1(1.5-6GHz) | 0V                      | -10V      | -32V      |  |

| 2(5-10GHz)  | 0V                      | -30V      | 0V        |  |

| 2(9-18GHz)  | 0V                      | 0V        | 0V        |  |

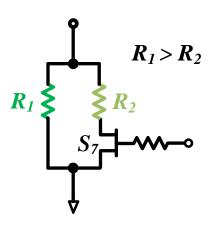

## Reconfigurable Dumping Load

- Reconfigurable Gate Bias Choke Module and dumping load module

- The optimization of the reconfigurable module for input matching in three modes.

- High Efficency NDPA Design Challenges

- PCPCT Design Details

- FRDPA Design Details

- Demonstration of GaN-based FRDPA

- Conclusion

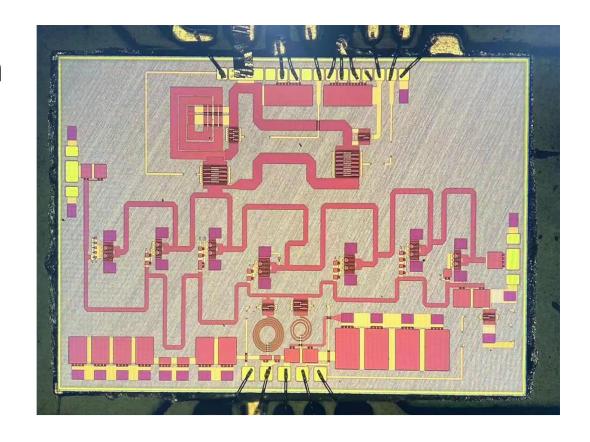

- Die micrograph

- Area with PADs: 3.76mm x 2.4mm

- Technology

- 0.25 µm GaN HEMT

- $-f_{\tau}$  = 25 GHz

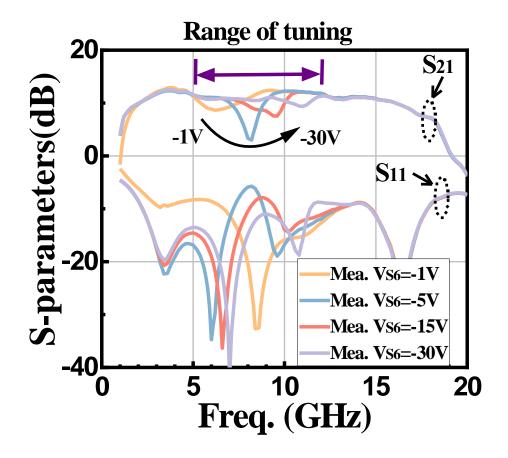

Minimize the discrepancy between the simulated model and the measured performance by the tuning switch the control voltage.

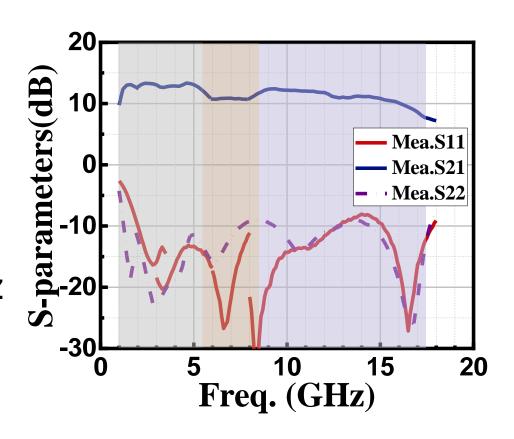

## • S<sub>21</sub>

- ->12dB@1.5-6GHz

- > 11dB@6-9GHz

- ->10.5dB@9-17GHz

- S<sub>11</sub>&S<sub>22</sub>

- <-7dB@1.5-6GHz& <-11dB@1.5-6GHz

- -<-12dB@6-9GHz&<-9.5dB@6-9GHz

- <-9dB@9-17GHz& <-9.5dB@9-17GHz</p>

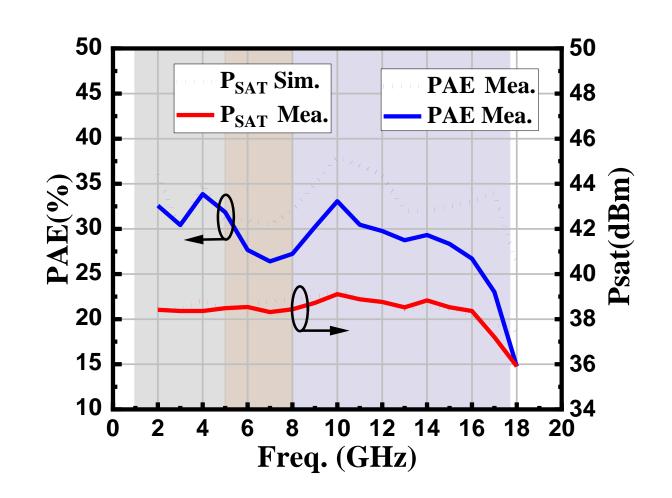

## • PAE<sub>max</sub>

- ->31%@2-6GHz

- ->27%@6-9GHz

- ->23.5%@9-17GHz

- ->38.1dBm@2-6GHz

- ->38.2dBm@6-9GHz

- > 37.1dBm @9-17GHz

## IMS Demonstration of GaN-based FRDPA Connecting Minds. Exchanging Ideas.

### – Comparison

| Parametric | Technology   | Freq.BW<br>(GHz) | Gain (dB)     | Supply<br>(V) | Total Gate<br>width(mm) | P <sub>sat</sub><br>(dBm) | PAE (%)   | Average<br>PAE* (%) |

|------------|--------------|------------------|---------------|---------------|-------------------------|---------------------------|-----------|---------------------|

| [3] IMS    | QGaN15       | 4-16             | 15.8-<br>17.5 | 18            | 1.05                    | 33.8-<br>35.4             | 11.8-33.9 | 20                  |

| [4] TMTT   | 0.25μm GaN   | 6-18             | 10±2          | 30            | 6                       | 38.7-<br>41.2             | 13.6-33.8 | 24                  |

| [7] IMS    | 0.2 um AlGaN | 2-20             | 9.7           | 30            | 6                       | 39.9-<br>43.4             | 15.3-35.7 | 26                  |

|            |              | 2-6              | 12.9          |               |                         | 38.1-<br>38.8             | 31-35     |                     |

| This work  | 0.25µm GaN   | 6-9              | 11.2          | 28            | 2.02                    | 38.2-<br>38.6             | 27-30     | 28                  |

|            | 9            | 9-17             | 11.1          |               |                         | 37.1-<br>39.2             | 23.5-34   |                     |

- High Efficency NDPA Design Challenges

- PCPCT Design Details

- FRDPA Design Details

- Demonstration of GaN-based FRDPA

- Conclusion

## Conclusion

A GaN-based FRDPA is designed and fabricated.

PCPCT and reconfigurable module is proposed.

0.25 µm GaN HEMT.

Ultra-wideband from 1.5 to 17 GHz.

## Thank You!

The following are the authors' emails. Questions are welcome. chenshijie3018@163.com, yongwang@uestc.edu.cn