# Equalization Tuning of the PCle Physical Layer by Using Machine Learning in Industrial Post-silicon Validation

F. E. Rangel-Patiño<sup>1,2</sup>, A. Viveros-Wacher<sup>2</sup>, C. Rajyaguru<sup>3</sup>, E. A. Vega-Ochoa<sup>2</sup>, S. D. Rodriguez-Saenz<sup>2</sup>, J. L. Silva-Cortes<sup>2</sup>, H. Shival<sup>3</sup>, and J. E. Rayas-Sánchez<sup>1</sup>

<sup>1</sup>Department of Electronics, Systems, and Informatics, ITESO – The Jesuit University of Guadalajara, Tlaquepaque, Jalisco, 45604 Mexico

<sup>2</sup>Intel Corp. Zapopan, Jalisco, 45019 Mexico <sup>3</sup>Intel Corp. Folsom, CA, 95630 USA

#### **Outline**

- Introduction to PCIe PHY tuning

- A machine learning (ML) proposal

- Unsupervised and supervised ML

- PHY tuning and optimization

- Clustering and GPR modeling results

- PHY optimization formulation and results

- Conclusions

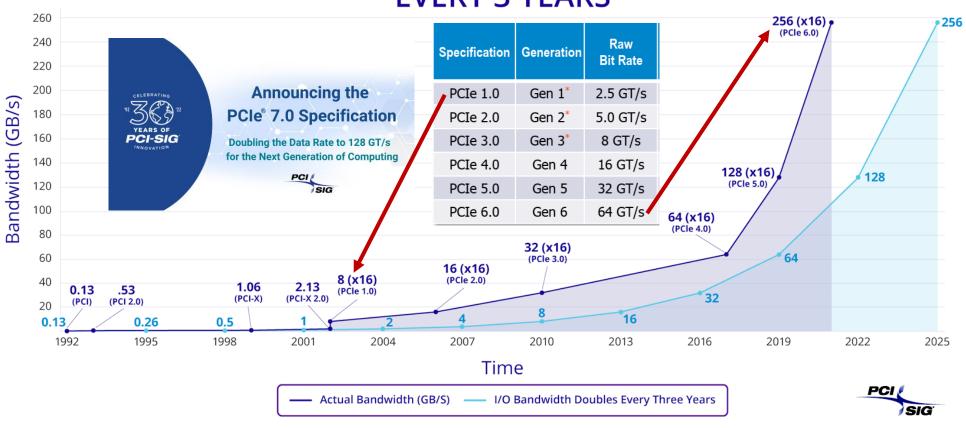

#### The Journey of PCIe

Servers

Storage

Communications

Embedded

#### **⊘ I/O BANDWIDTH DOUBLES** EVERY 3 YEARS

Continuous improvement in data rates and usage models

Usage of PCIe technology continues to grow driven by BW demand

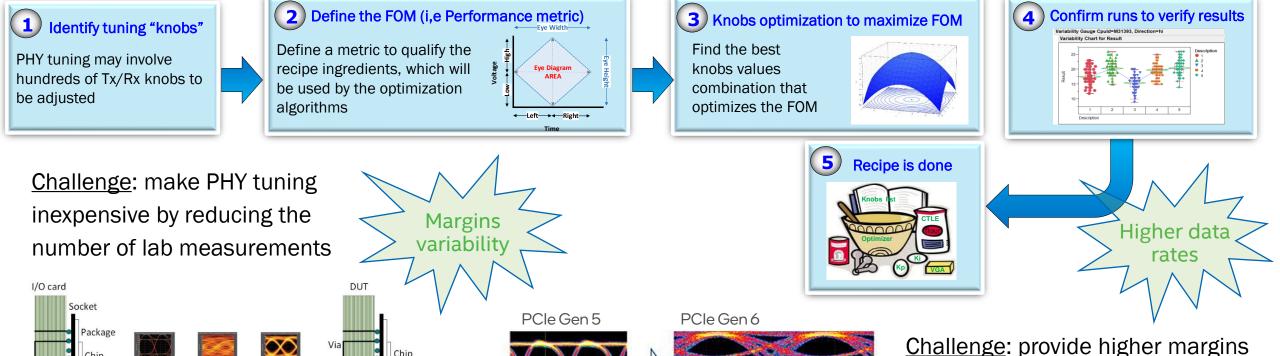

# **PCIe Tuning Complexity**

- PHY tuning is very time consuming

- Typically based on exhaustive search methods to find the "best" Tx and Rx EQ settings

Connector

Backplane (channel)

on a wide variety of devices and

channels, along with process,

voltage and temperature (PVT)

variation

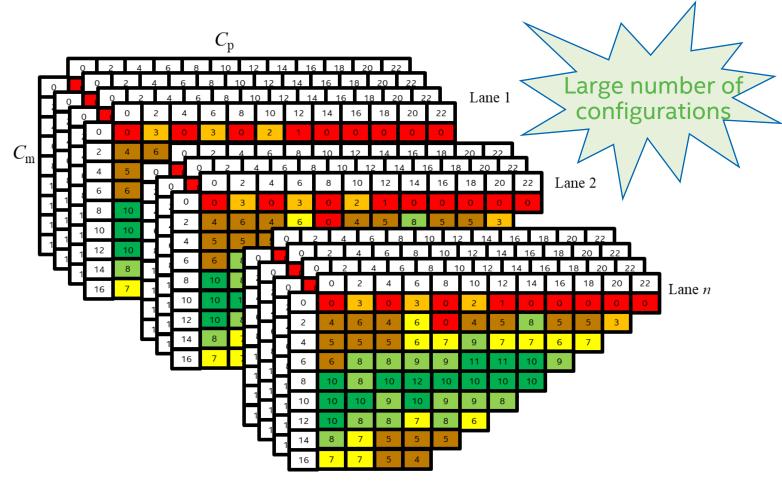

## PCIe Tuning Complexity (cont.)

Many EQs maps, obtained from lab measurements, are typically employed

for different lanes, channels, PVT, etc.

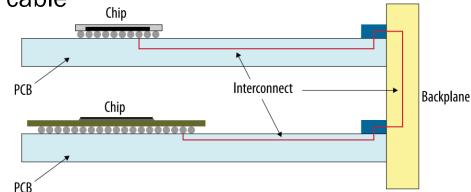

Short to mid range interconnect chip to chip within a PCB

Mid to long range interconnect chip to chip across a backplane/midplane or a cable

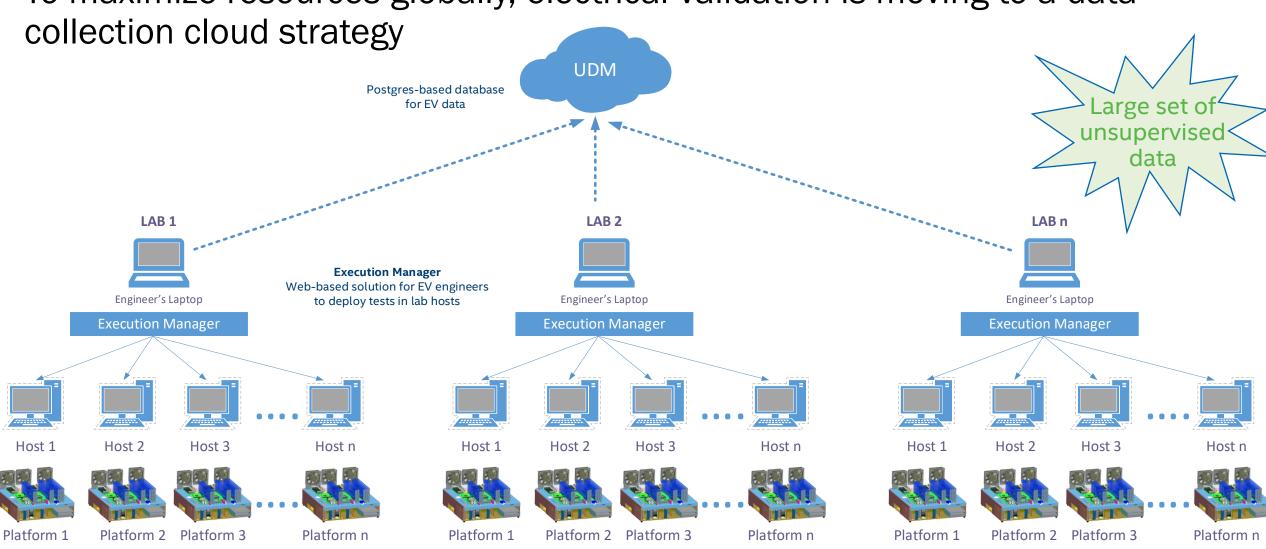

#### **Post-Silicon Validation Cloud Tools**

To maximize resources globally, electrical validation is moving to a data-

## A Machine Learning Proposal

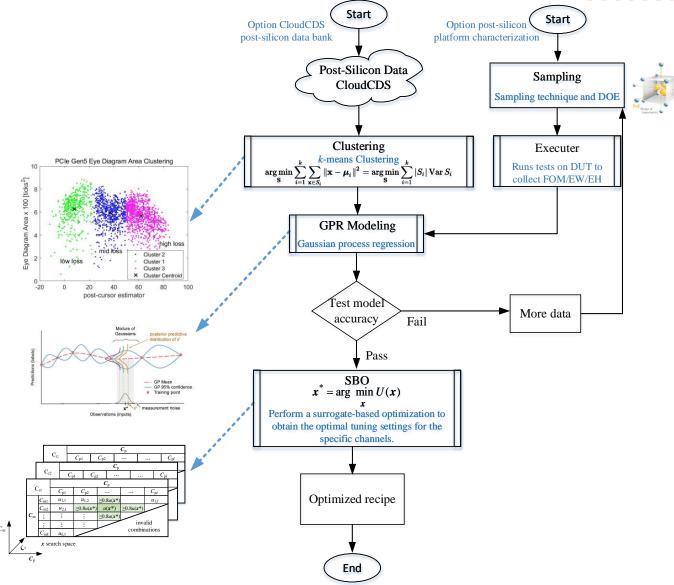

- We propose a combination of unsupervised and supervised ML techniques to tune high-speed PCle5 NRZ and PCle6 PAM4 designs on a real post-Si platform

- Our proposal helps to:

- Eliminate manual PHY tuning efforts

- Reduce engineering and debugging costs

- Accelerate post-silicon validation

- We aim at increasing accuracy and robustness of the solution by using massive and diverse post-Si validation cloud data

## A Machine Learning Proposal (cont.)

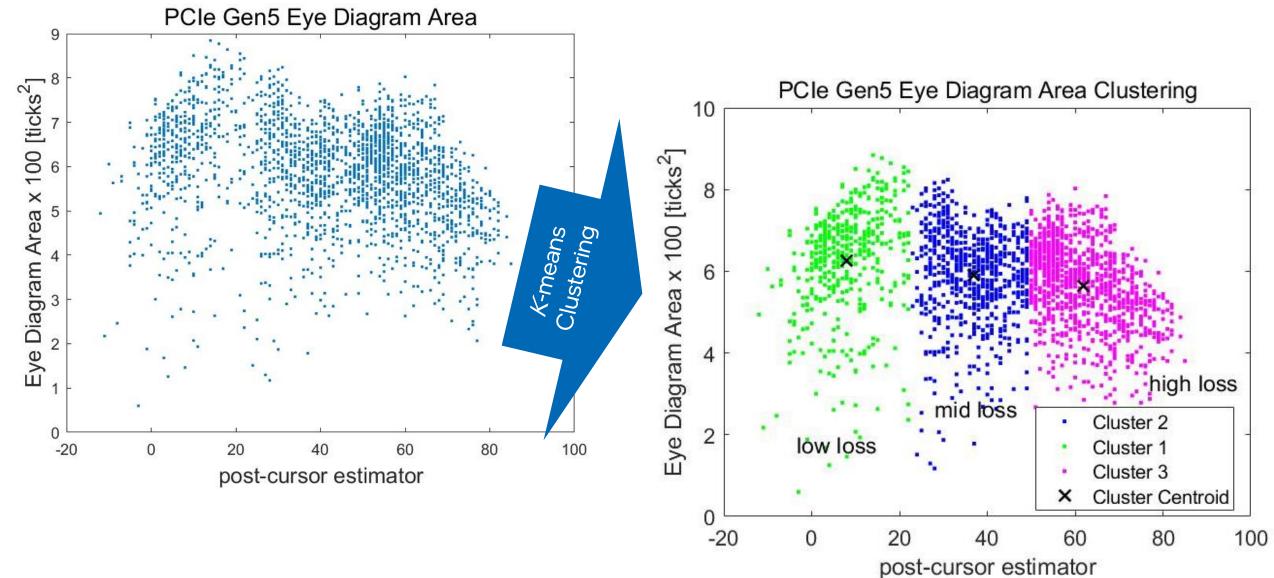

- We use unsupervised ML modeling to cluster prior SMV and EQ data

- The clustered data segments are used to train supervised ML models

- These models approximate margins for a given combination of PHY parameters

- The models are used to find optimal PHY tuning parameters through a surrogate-based optimization (SBO)

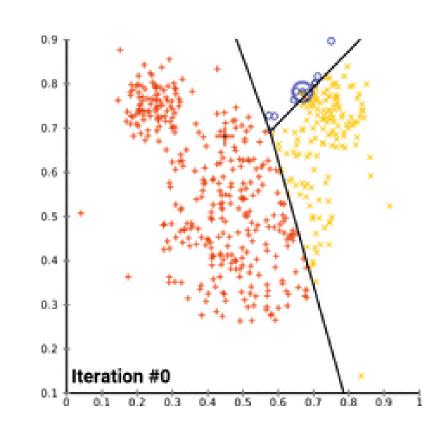

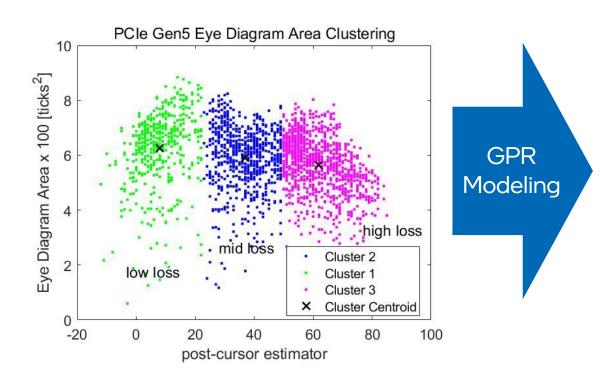

## **Unsupervised ML: Clustering**

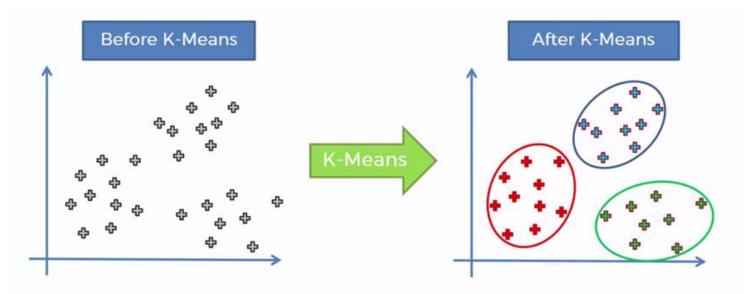

- Unsupervised ML algorithms learn patterns from untagged data

- Clustering is the task of grouping similar data points

- We use the k-means clustering algorithm that partitions n observations into k clusters

## **Unsupervised ML: Clustering (cont.)**

Given a set of observations  $(x_1, x_2, ..., x_n)$ , where each observation is a d-dimensional real vector, k-means clustering aims to partition the n observations into  $k (\leq n)$  sets  $S = \{S_1, S_2, ..., S_k\}$  to minimize the within-cluster variance

We solve:

$$rg\min_{\mathbf{S}} \sum_{i=1}^k \sum_{\mathbf{x} \in S_i} \|\mathbf{x} - oldsymbol{\mu}_i\|^2 = rg\min_{\mathbf{S}} \sum_{i=1}^k |S_i| \operatorname{Var} S_i$$

where  $\mu_i$  is the mean of points in  $S_i$

By Chire - Own work, CC BY-SA 4.0, https://commons.wikimedia.org/w/index.php?curid=59409335

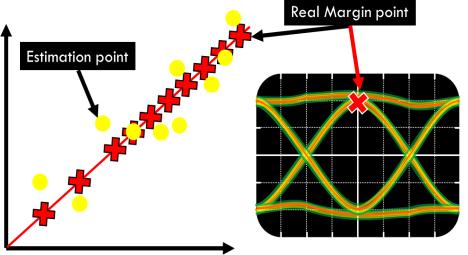

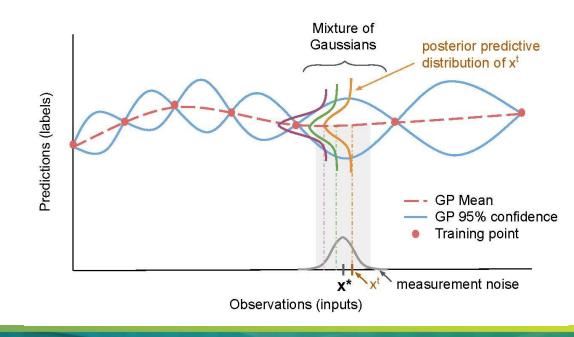

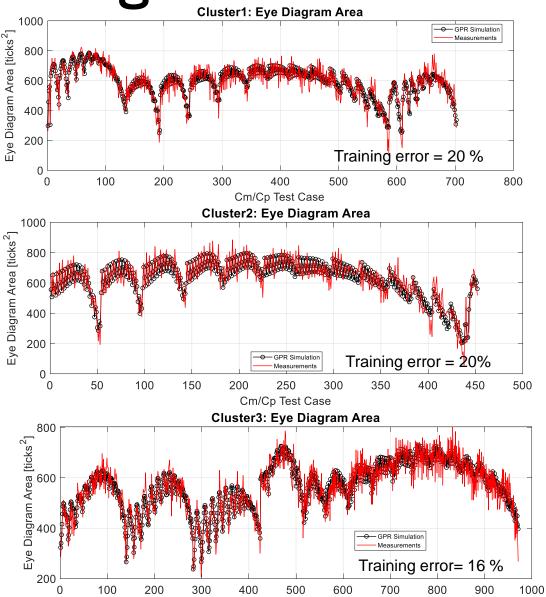

#### Supervised ML: GPR Modeling

- We use supervised machine learning regression to model eye margins

- Given the large statistical fluctuations in post-Si electrical validation measurements, we use Gaussian process regression (GPR)

- GPR aims to predict not only the outputs based on inputs, but also their variability (probability distribution)

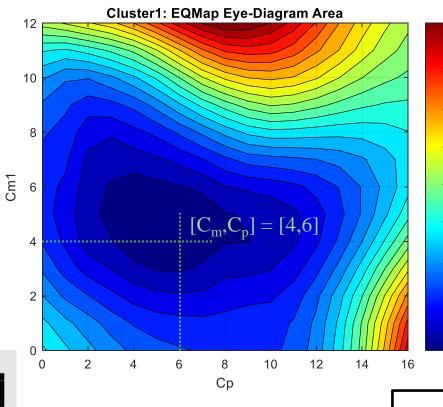

#### **Clustering Results**

#### **GPR Modeling Results**

Cm/Cp Test Case

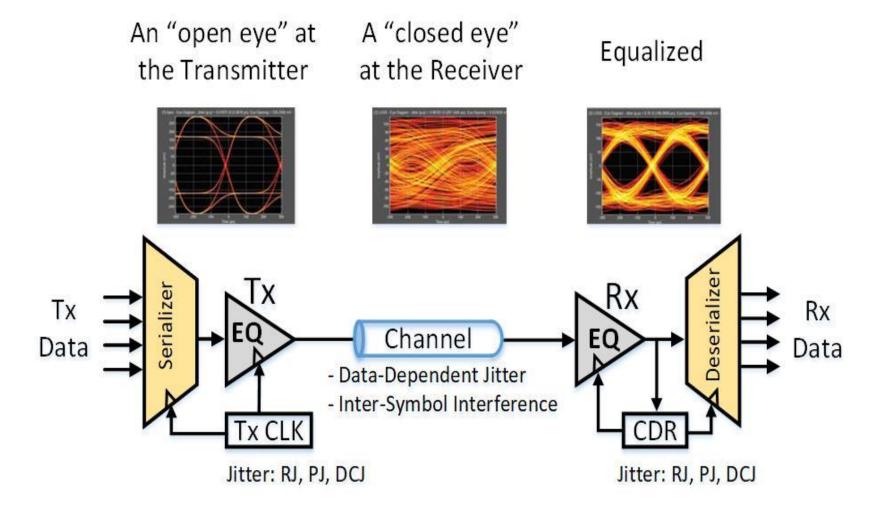

# **Equalization: PCIe PHY Tuning**

Equalization settings need to be optimized for best link performance

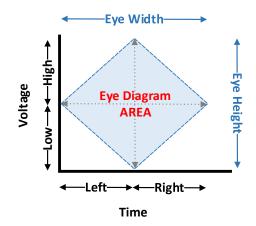

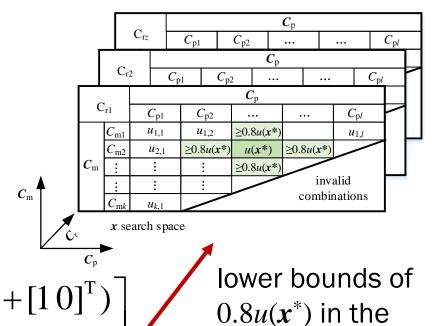

# SBO Exploiting GPR Models

•  $R_{\rm m}\in\Re^2$ : GPR response using functional margins

$$\mathbf{R}_{\mathrm{m}} = \mathbf{R}_{\mathrm{m}}(\mathbf{x}, \boldsymbol{\psi}, \boldsymbol{\delta}) = \begin{bmatrix} e_{\mathrm{w}}(\mathbf{x}, \boldsymbol{\psi}, \boldsymbol{\delta}) & e_{\mathrm{h}}(\mathbf{x}, \boldsymbol{\psi}, \boldsymbol{\delta}) \end{bmatrix}^{\mathrm{T}} - \mathbf{e}_{\mathrm{h}}(\mathbf{x}, \boldsymbol{\psi}, \boldsymbol{\delta})$$

- We solve by direct optimization  $x^* = \arg \min U(x)$  where x has the EQ settings

- Our unconstrained objective function is

$$U(\mathbf{x}) = -[e_{w}(\mathbf{x})][e_{h}(\mathbf{x})] + L(\mathbf{x}) \left[ \frac{|u(\mathbf{x}^{(0)})|}{\max\{l(\mathbf{x}^{(0)})\}} \right]$$

where  $x^{(0)}$  is the starting point and L(x) is a corner limits penalty function defined as

$$L(x) = \max\{0, \max\{l(x)\}\}\$$

with

$$l(\mathbf{x}) = 0.8u(\mathbf{x})\begin{bmatrix} 1 & 1 \\ 1 & 1 \end{bmatrix} - \begin{bmatrix} u(\mathbf{x} - [10]^T) & u(\mathbf{x} + [10]^T) \\ u(\mathbf{x} - [01]^T) & u(\mathbf{x} + [01]^T) \end{bmatrix}$$

vicinity of  $x^*$

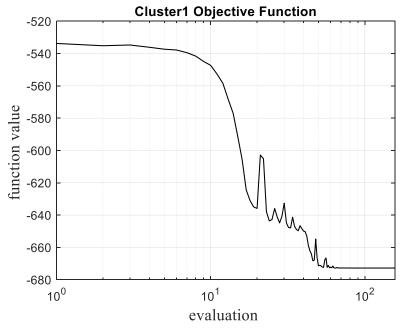

#### SBO PCIe PHY Tuning Results

-250

-300

-350

-450

-500

-550

-650

coefficients

10<sup>0</sup>

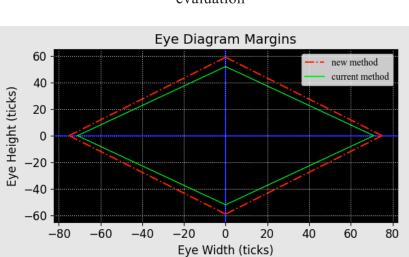

#### Current method takes days, while new method takes a few hours

#### PCIe Gen5 - FIR EQ Opt. Summary

**Cluster1 Normalized Coefficients Responses**

evaluation

Cluster 1:  $x^* = [4 \ 6]^T$ ,  $U(x^*) = -672.77$

Cluster 2:  $x^* = [4 \ 8]^T$ ,  $U(x^*) = -719.35$

Cluster 3:  $x^* = [5 \ 4]^T$ ,  $U(x^*) = -688.73$

10<sup>2</sup>

#### Conclusions

- We propose a new methodology for PCIe link equalization

- Our methodology can be applied to other interfaces for PHY optimization

- We use ML techniques to cluster post-silicon data from different channels and feed those clusters to a GPR-based metamodel for each channel

- We use SBO to find the optimal PHY settings

- A significant increase in eye diagram margins is achieved, accelerating the PHY tuning process